Книга: Advanced PIC Microcontroller Projects in C

2.1.3 The Configuration Registers

2.1.3 The Configuration Registers

PIC18F452 microcontrollers have a set of configuration registers (PIC16-series microcontrollers had only one configuration register). Configuration registers are programmed during the programming of the flash program memory by the programming device. These registers are shown in Table 2.2. these registers are given in Table 2.3. Some of the more important configuration registers are described in this section in detail.

Table 2.2: PIC18F452 configuration registers

| File Name | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default/Unprogrammed Value | |

|---|---|---|---|---|---|---|---|---|---|---|

| 300001h | CONFIG1H | — | — | OSCSEN# | — | — | FOSC2 | FOSC1 | FOSC0 | --1--111 |

| 300002h | CONFIG2L | — | — | — | — | BORV1 | BORV0 | BOREN | PWRTEN# | ---- 1111 |

| 300003h | CONFIG2H | — | — | — | — | WDTPS2 | WDTPS1 | WDTPS0 | WDTEN | ---- 1111 |

| 300005h | CONFIG3H | — | — | — | — | — | — | — | CCP2MX | ---- ---1 |

| 300006h | CONFIG4L | DEBUG | — | — | — | — | LVP | — | STVREN1 | --- -1-1 |

| 300008h | CONFIG5L | — | — | — | — | CP3 | CP2 | CP1 | CP0 | ---- 1111 |

| 300009h | CONFIG5H | CPD | CPB | — | — | — | — | — | — | 11-- ---- |

| 30000Ah | CONFIG6L | — | — | — | — | WRT3 | WRT2 | WRT1 | WRT0 | ---- 1111 |

| 30000Bh | CONFIG6H | WRTD | WRTB | WRTC | — | — | — | — | — | 111- ---- |

| 30000Ch | CONFIG7L | — | — | — | — | EBTR3 | EBTR2 | EBTR1 | EBTR0 | ---- 1111 |

| 30000Dh | CONFIG7H | — | EBTRB | — | — | — | — | — | — | -1----- |

| 3FFFFEh | DEVID1 | DEV2 | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0 | (1) |

| 3FFFFFh | DEVID2 | DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3 | 0000 0100 |

Legend: x = unknown, u = unchanged, – = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as ‘0’.

Table 2.3: PIC18F452 configuration register descriptions

| Configuration bits | Description |

|---|---|

| OSCSEN | Clock source switching enable |

| FOSC2:FOSC0 | Oscillator modes |

| BORV1:BORV0 | Brown-out reset voltage |

| BOREN | Brown-out reset enable |

| PWRTEN | Power-up timer enable |

| WDTPS2:WDTPS0 | Watchdog timer postscale bits |

| WDTEN | Watchdog timer enable |

| CCP2MX | CCP2 multiplex |

| DEBUG | Debug enable |

| LVP | Low-voltage program enable |

| STVREN | Stack full/underflow reset enable |

| CP3:CP0 | Code protection |

| CPD | EEPROM code protection |

| CPB | Boot block code protection |

| WRT3:WRT0 | Program memory write protection |

| WRTD | EPROM write protection |

| WRTB | Boot block write protection |

| WRTC | Configuration register write protection |

| EBTR3:EBTR0 | Table read protection |

| EBTRB | Boot block table read protection |

| DEV2:DEV0 | Device ID bits (001 = 18F452) |

| REV4:REV0 | Revision ID bits |

| DEV10:DEV3 | Device ID bits |

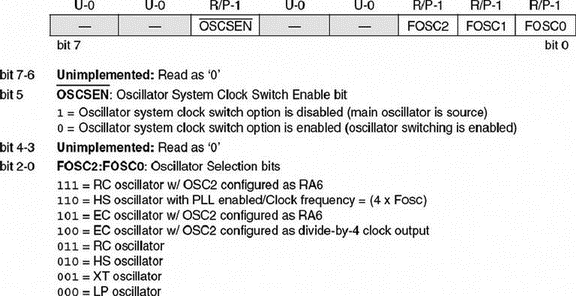

CONFIG1H

The CONFIG1H configuration register is at address 300001H and is used to select the microcontroller clock sources. The bit patterns are shown in Figure 2.6.

Figure 2.6: CONFIG1H register bits

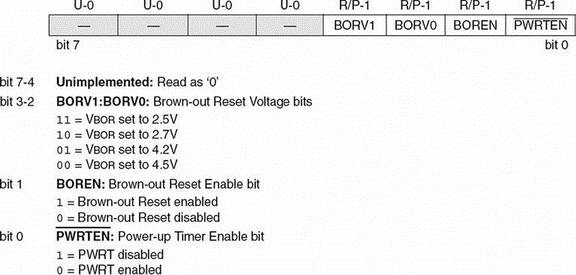

CONFIG2L

The CONFIG2L configuration register is at address 300002H and is used to select the brown-out voltage bits. The bit patterns are shown in Figure 2.7.

Figure 2.7: CONFIG2L register bits

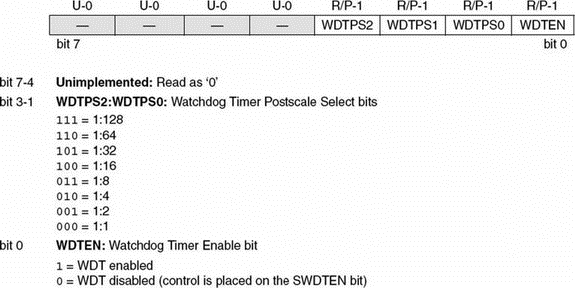

CONFIG2H

The CONFIG2H configuration register is at address 300003H and is used to select the watchdog operations. The bit patterns are shown in Figure 2.8.

Figure 2.8: CONFIG2H register bits

- 2.1.1 Program Memory Organization

- 2.1.2 Data Memory Organization

- 2.1.3 The Configuration Registers

- 2.1.4 The Power Supply

- 2.1.5 The Reset

- 2.1.6 The Clock Sources

- 2.1.7 Watchdog Timer

- 2.1.8 Parallel I/O Ports

- 2.1.9 Timers

- 2.1.10 Capture/Compare/PWM Modules (CCP)

- 2.1.11 Analog-to-Digital Converter (A/D) Module

- 2.1.12 Interrupts

- 2.1.4 The Power Supply

- 4.6.5 Other Views

- 4.4.4 The Dispatcher

- About the author

- Chapter 7. The state machine

- Appendix E. Other resources and links

- Example NAT machine in theory

- The final stage of our NAT machine

- Compiling the user-land applications

- The conntrack entries

- Untracked connections and the raw table

- Basics of the iptables command