Книга: 2.Внутреннее устройство Windows (гл. 5-7)

Ассоциативный буфер трансляции

Ассоциативный буфер трансляции

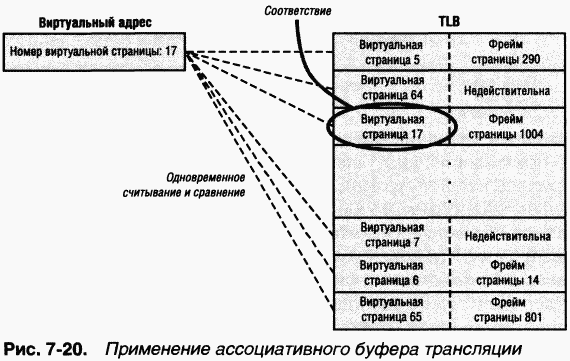

Как вы уже знаете, трансляция каждого адреса требует двух операций поиска: сначала нужно найти подходящую таблицу страниц в каталоге страниц, затем — элемент в этой таблице. Поскольку выполнение этих двух операций при каждом обращении по виртуальному адресу могло бы снизить быстродействие системы до неприемлемого уровня, большинство процессоров кэшируют транслируемые адреса, в результате чего необходимость в повторной трансляции при обращении к тем же адресам отпадает. Процессор поддерживает такой кэш в виде массива ассоциативной памяти, называемого ассоциативным буфером трансляции (translation look-aside buffer, TLB). Ассоциативная память вроде TLB представляет собой вектор, ячейки которого можно считывать и сразу сравнивать с целевым значением. B случае TLB вектор содержит сопоставления физических и виртуальных адресов для недавно использовавшихся страниц, а также атрибуты защиты каждой страницы, как показано на рис. 7-20. Каждый элемент TLB похож на элемент кэша, в метке которого хранятся компоненты виртуального адреса, а в поле данных — номер физической страницы, атрибуты защиты, битовый флаг Valid и, как правило, битовый флаг Dirty. Эти флаги отражают состояние страницы, которой соответствует кэшированный РТЕ. Если в PTE установлен битовый флаг Global (используется для страниц системного пространства, глобально видимых всем процессам), то при переключениях контекста элемент TLB не объявляется недействительным.

Часто используемым виртуальным адресам обычно соответствуют элементы в TLB, который обеспечивает чрезвычайно быструю трансляцию виртуальных адресов в физические, а в результате и быстрый доступ к памяти. Если виртуального адреса в TLB нет, он все еще может быть в памяти, но для его поиска понадобится несколько обращений к памяти, что увеличит время доступа. Если виртуальный адрес оказался в страничном файле или если диспетчер памяти изменил его РТЕ, диспетчер памяти должен явно объявить соответствующий элемент TLB недействительным. Если процесс повторно обращается к нему, генерируется ошибка страницы, нужная страница загружается обратно в память и для нее вновь создается элемент TLB.

Диспетчер памяти по возможности обрабатывает аппаратные и программные PTE одинаково. Так, при объявлении недействительного PTE действительным диспетчер памяти вызывает функцию ядра, которая обеспечивает аппаратно-независимую загрузку в TLB нового PTE. B х86-системах эта функция заменяется командой NOP, поскольку процессоры типа x86 самостоятельно загружают данные в TLB.

- Введение в диспетчер памяти

- Компоненты диспетчера памяти

- Внутренняя синхронизация

- Конфигурирование диспетчера памяти

- Исследование используемой памяти

- Сервисы диспетчера памяти

- Большие и малые страницы

- Резервирование и передача страниц

- Блокировка памяти

- Гранулярность выделения памяти

- Разделяемая память и проецируемые файлы

- Защита памяти

- Запрет на выполнение

- Программный вариант DEP

- Копирование при записи

- Диспетчер куч

- Типы куч

- Структура диспетчера кучи

- Синхронизация доступа к куче

- Ассоциативные списки

- Куча с малой фрагментацией

- Средства отладки

- Pageheap

- Address Windowing Extensions

- Системные пулы памяти

- Настройка размеров пулов

- Мониторинг использования пулов

- Ассоциативные списки

- Утилита Driver Verifier

- Настройка и инициализация Driver Verifier

- Special Pool (Особый пул)

- Pool Tracking (Слежение за пулом)

- Force IRQL Checking (Обяз. проверка IRQL)

- Low Resources Simulation (Нехватка ресурсов)

- Структуры виртуального адресного пространства

- Структуры пользовательского адресного пространства на платформе x86

- Структура системного адресного пространства на платформе x86

- Пространство сеанса на платформе x86

- Системные PTE

- Структуры 64-разрядных адресных пространств

- Трансляция адресов

- Трансляция виртуальных адресов на платформе x86

- Каталоги страниц

- Страницы таблиц и PTE

- Адрес байта в пределах страницы

- Ассоциативный буфер трансляции

- Physical Address Extension (PAE)

- Трансляция виртуальных адресов на платформе IA64

- Трансляция виртуальных адресов на платформе x64

- Обработка ошибок страниц

- Недействительные PTE

- Прототипные PTE

- Операции ввода-вывода, связанные с подкачкой страниц

- Конфликты ошибок страницы

- Страничные файлы

- Дескрипторы виртуальных адресов

- Объекты-разделы

- Рабочие наборы

- Подкачка по требованию

- Средство логической предвыборки

- Правила размещения

- Управление рабочими наборами

- Диспетчер настройки баланса и подсистема загрузки-выгрузки

- Системный рабочий набор

- База данных PFN

- Динамика списков страниц

- Подсистема записи модифицированных страниц

- Структуры данных PFN

- Уведомление о малом или большом объеме памяти

- Оптимизаторы памяти — миф или реальность?

- Резюме

- 1.6 Драйверы и буферы ввода-вывода

- 5.2.2. Ассоциативный чертеж

- 14.2. Переполнение буфера

- Буфер обмена и команды для работы с ним

- Использование буфера обмена

- 9.3.1.2. Буферирование каналов

- Конфигурация Exim для ретрансляции писем

- Конфигурация Postfix для ретрансляции писем

- Буферный кэш

- Внутренняя структура буферного кэша

- Буферизация

- Буферы и заголовки буферов