Книга: 2.Внутреннее устройство Windows (гл. 5-7)

Страницы таблиц и PTE

Страницы таблиц и PTE

Элементы каталога страниц (page directory entries, PDE), принадлежащего процессу, указывают на индивидуальные таблицы страниц, которые состоят из массива РТЕ. Поле индекса таблицы страницы в виртуальном адресе (как показано на рис. 7-17) определяет PTE нужной страницы данных. B x86-системах размер этого индекса равен 10 битам (в PAE — 9), что позволяет ссылаться на 1024 4-байтных PTE (в PAE — на 512 8-байтных PTE). Ho, поскольку 32-разрядная Windows предоставляет процессам 4-гигабайтное закрытое адресное пространство, для проецирования всего адресного пространства одной таблицы страниц мало. Чтобы подсчитать количество таблиц страниц, нужных для проецирования всех 4 Гб виртуального адресного пространства, поделите 4 Гб на объем виртуальной памяти, описываемой одной таблицей. Помните, что каждая таблица страниц в х86-системах определяет страницы данных суммарным размером в 4 Мб (в PAE — 2 Мб). Поэтому для проецирования всех 4 Гб адресного пространства требуется 1024 (4 Гб / 4 Мб) таблицы страниц, а в РАЕ-системах — 2048 (4 Гб / 2 Мб).

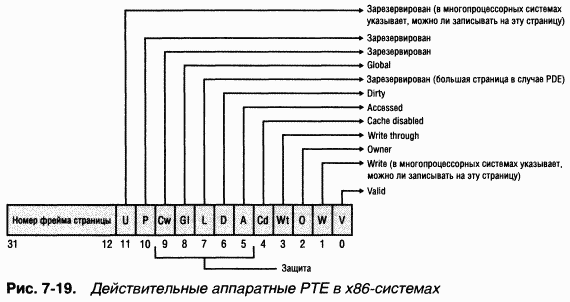

Для изучения PTE используйте команду !pte отладчика ядра (см. эксперимент «Трансляция адресов» далее в этой главе). Действительные PTE (здесь мы обсуждаем именно их — о недействительных PTE см. далее) состоят из двух основных полей (рис. 7-19): поля PFN физической страницы с данными (или физического адреса страницы в памяти) и поля флагов, описывающих состояние и атрибуты защиты страницы.

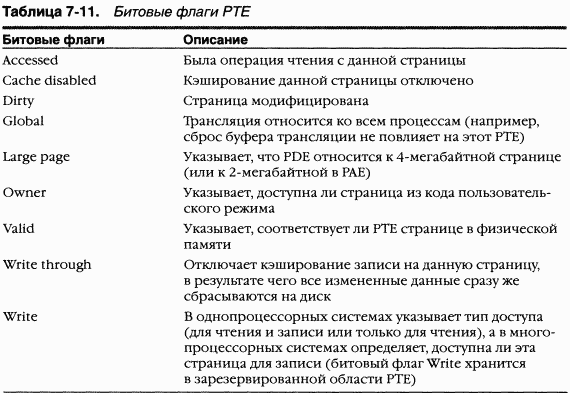

Как вы еще увидите, битовые флаги, помеченные как зарезервированные рис. 7-19), используются, только если PTE недействителен (флаги интерпретируются программно). Аппаратно определяемые битовые флаги действительного PTE перечислены в таблице 7-11.

B х86-системах аппаратный PTE содержит биты Dirty и Accessed. Бит Accessed равен 0, если данные физической страницы, представляемой РТЕ, не были считаны или записаны. Процессор устанавливает этот бит при первой операции чтения или записи страницы. Бит Dirty устанавливается только после первой записи на страницу. Кроме того, бит Write обеспечивает защиту страницы: если он сброшен, страница доступна только для чтения, а если он установлен, страница доступна как для чтения, так и для записи. Когда поток пытается что-то записать на страницу со сброшенным битом Write, возникает исключение управления памятью, и обработчик, принадлежащий диспетчеру памяти, решает, может ли поток записывать данные на эту страницу (если она, например, помечена как копируемая при записи) или следует сгенерировать нарушение доступа.

Для аппаратных PTE в многопроцессорных х86-системах предусматривается дополнительный бит Write, реализуемый программно и предотвращающий остановку системы при сбросе кэша PTE (также называемого ассоциативным буфером трансляции). Этот бит указывает, что страница была модифицирована другим процессором.

- Введение в диспетчер памяти

- Компоненты диспетчера памяти

- Внутренняя синхронизация

- Конфигурирование диспетчера памяти

- Исследование используемой памяти

- Сервисы диспетчера памяти

- Большие и малые страницы

- Резервирование и передача страниц

- Блокировка памяти

- Гранулярность выделения памяти

- Разделяемая память и проецируемые файлы

- Защита памяти

- Запрет на выполнение

- Программный вариант DEP

- Копирование при записи

- Диспетчер куч

- Типы куч

- Структура диспетчера кучи

- Синхронизация доступа к куче

- Ассоциативные списки

- Куча с малой фрагментацией

- Средства отладки

- Pageheap

- Address Windowing Extensions

- Системные пулы памяти

- Настройка размеров пулов

- Мониторинг использования пулов

- Ассоциативные списки

- Утилита Driver Verifier

- Настройка и инициализация Driver Verifier

- Special Pool (Особый пул)

- Pool Tracking (Слежение за пулом)

- Force IRQL Checking (Обяз. проверка IRQL)

- Low Resources Simulation (Нехватка ресурсов)

- Структуры виртуального адресного пространства

- Структуры пользовательского адресного пространства на платформе x86

- Структура системного адресного пространства на платформе x86

- Пространство сеанса на платформе x86

- Системные PTE

- Структуры 64-разрядных адресных пространств

- Трансляция адресов

- Трансляция виртуальных адресов на платформе x86

- Каталоги страниц

- Страницы таблиц и PTE

- Адрес байта в пределах страницы

- Ассоциативный буфер трансляции

- Physical Address Extension (PAE)

- Трансляция виртуальных адресов на платформе IA64

- Трансляция виртуальных адресов на платформе x64

- Обработка ошибок страниц

- Недействительные PTE

- Прототипные PTE

- Операции ввода-вывода, связанные с подкачкой страниц

- Конфликты ошибок страницы

- Страничные файлы

- Дескрипторы виртуальных адресов

- Объекты-разделы

- Рабочие наборы

- Подкачка по требованию

- Средство логической предвыборки

- Правила размещения

- Управление рабочими наборами

- Диспетчер настройки баланса и подсистема загрузки-выгрузки

- Системный рабочий набор

- База данных PFN

- Динамика списков страниц

- Подсистема записи модифицированных страниц

- Структуры данных PFN

- Уведомление о малом или большом объеме памяти

- Оптимизаторы памяти — миф или реальность?

- Резюме

- CHAPTER 20 Remote File Serving with FTP

- Системные PTE

- Прототипные PTE

- Информация заголовочной страницы (Database header)

- Размер страницы базы данных

- Дополнительные национальные кодовые страницы и порядки сортировки

- Безопасная работа с внешними таблицами

- Модификация системных таблиц

- Безопасность временных таблиц

- Безопасность внешних таблиц. Параметр EXTERNAL FILE DIRECTORY

- 6.5 Хост в таблице маршрутизации IP

- Chapter 5. Preparations