Книга: Аппаратные интерфейсы ПК. Энциклопедия

6.1.2. Прямой доступ к памяти — DMA

6.1.2. Прямой доступ к памяти — DMA

Прямой доступ к памяти позволяет абоненту шины организовывать обмен данными между своим регистром и памятью под управлением контроллера DMA, минуя центральный процессор. До выполнения обмена канал DMA должен быть инициализирован — задан начальный адрес и размер пересылаемого блока памяти, направление и режим обмена. После инициализации канала обмен выполняется по инициативе ПУ.

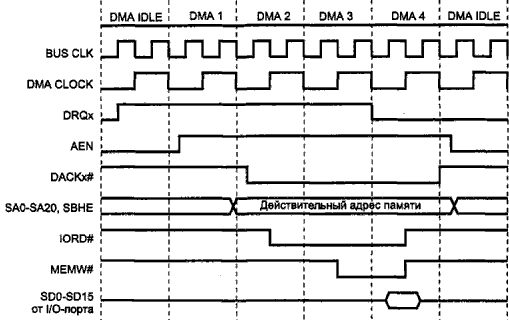

Для интерфейса ПУ каждый канал DMA представляется парой сигналов: запрос обмена — DRQx и подтверждение обмена — DACKx#, где x — номер используемого канала. На рис. 6.3 приведена диаграмма стандартного цикла передачи байта (для 8-битного канала) или слова (для 16-битного) от ПУ в память по каналу DMA. Цикл передачи блока байтов или слов в память будет выглядеть следующим образом.

1. По сигналу DRQx контроллер DMA запрашивает управление шиной и дожидается его предоставления процессором (и другими контроллерами шины).

2. Контроллер выставляет адрес ячейки памяти и формирует в одном цикле шины сигналы IOR#, DACKx# и MEMW#. Адрес на всех линиях, включая LA[23:17], действителен во время всего цикла (защелкивание не требуется), BALE=H в течение всего цикла. Сигнал DACKx# указывает на то, что операция выполняется для канала x, a IOR# — на направление в канале (для пересылки из памяти в канал использовался бы сигнал IOW#). Чтобы по сигналу IOR# не было ложного чтения (по IOW# — ложной записи) порта, адрес которого совпадает с адресом памяти, присутствующим в цикле DMA, контроллер высоким уровнем сигнала AEN запрещает портам дешифрацию адреса. Байт, считанный из ПУ, в том же цикле шины записывается в ячейку памяти.

3. Контроллер модифицирует счетчик адреса и повторяет шаги 1–2 для каждого следующего сигнала DRQx, пока не будет исчерпан счетчик циклов. В последнем цикле обмена контроллер формирует общий сигнал окончания TC (Terminate Count), который может быть использован устройством для формирования сигнала аппаратного прерывания.

Рис. 6.3. Цикл обмена DMA

Диаграмма обратной пересылки (из памяти в ПУ) отличается только тем, что на месте сигнала IOR# будет сигнал MEMR#, а на месте MEMW# — сигнал IOW#. Направление обмена и параметры режима задаются программированием контроллера DMA.

Цикл DMA, и так довольно длинный, может быть растянут устройством с помощью сигнала IOCHRDY (но сократить его сигналом 0WS# невозможно). Запрашивать удлинение цикла может только адресованная память — подразумевается, что когда ПУ выставляет запрос DRQx, оно уже должно быть готово к обмену.

На 16-битной шине ISA доступно 7 каналов DMA: четыре 8-битных (номера 0–3) и три 16-битных (5–7), подключенные к первичному и вторичному контроллерам соответственно. Канал 4 используется для каскадирования (соединения контроллеров). На 8-битном слоте доступны только четыре 8-битных канала (в XT только 3 — канал 0 требовался для регенерации памяти).

Кроме приведенного на рисунке режима одиночной передачи возможны и иные, описанные в п. 12.4.

Напомним, что по 8-битным каналам DMA за один сеанс настройки контроллера можно передавать не более 64К байт данных, начинающихся с любого адреса (но не пересекая границ страниц, см. п. 12.3.2 и 12.5). По 16-битным каналам за сеанс можно передавать не более 64К слов данных, начинающихся с четного адреса, и границы страниц иные. Используя DMA в режимах, отличных от одиночного, длительность непрерывной передачи не должна превышать 15 мкс (для обеспечения регенерации памяти).

- 12.4. Прямой доступ к памяти — DMA

- 6.2.7. Прямой доступ к памяти, эмуляция ISA DMA (PC

- Что делать, если при установке принтера появляется сообщение Невозможно завершение операции. Подсистема печати недоступн...

- 9.4. Права доступа к squid

- 3.2.1.2. Начальное выделение памяти: malloc()

- Глава 29 Доступ к канальному уровню

- 10.5. Транзакции и пути доступа меню

- Настройка доступа пользователей к рабочей книге

- 3.5 Проблемы доступа при использовании нескольких протоколов

- Доступ к существующим рабочим областям для документов

- Неисправности оперативной памяти

- Как работает модуль оперативной памяти