Книга: Аппаратные интерфейсы ПК. Энциклопедия

6.4. Интерфейс LPC

6.4. Интерфейс LPC

Интерфейс LPC (Low Pin Count — малое число выводов) предназначен для локального подключения устройств, ранее использовавших шину X-Bus или ISA: контроллеров НГМД, последовательных и параллельных портов, клавиатуры, аудиокодека, BIOS и т.п. Введение нового интерфейса обусловлено изживанием шины ISA с ее большим числом сигналов и неудобной асинхронностью. Интерфейс обеспечивает те же циклы обращения, что и ISA: чтение-запись памяти и ввода-вывода, DMA и прямое управление шиной (bus mastering). Устройства могут вырабатывать запросы прерываний. В отличие от ISA/X-Bus с их 24-битной шиной адреса, обеспечивающей адресацию лишь в пределах первых 16 Мбайт памяти, интерфейс LPC имеет 32-битную адресацию памяти, что обеспечивает доступ к 4 Гбайт памяти. 16-битная адресация портов обеспечивает доступ ко всему пространству 64 К портов. Интерфейс синхронизирован с шиной PCI, но устройства могут вводить произвольное число тактов ожидания. Интерфейс программно прозрачен — как и для ISA/X-Bus, не требует каких-либо драйверов. Контроллер интерфейса LPC является устройством-мостом PCI. По пропускной способности интерфейс практически эквивалентен этим шинам. В спецификации LPC 1.0 приводится расчет пропускной способности интерфейса и устройств, его использующих. При наличии буферов FIFO интерфейс наиболее выгодно использовать в режиме DMA. В этом случае главным потребителем будет LPT-порт — при скорости передачи данных 2 Мбайт/с он займет 47% полосы интерфейса. Следующим будет инфракрасный порт — 4 Мбит/с (11,4%). Остальным устройствам (контроллер НГМД, СОМ-порт, аудиокодек) требуются еще меньшие доли, в результате они занимают до 75% полосы при одновременной работе. Таким образом, перевод этих устройств с ISA/X-Bus на LPC не должен вызывать проблем производительности более острых, чем были на старых шинах.

Интерфейс имеет всего 7 обязательных сигналов:

? LAD[3:0] — двунаправленная мультиплексированная шина данных;

? LFRAME# — индикатор начала и конца цикла, управляемый хостом;

? LRESET# — сигнал сброса, тот же, что и RST# на шине PCI;

? LCLK — синхронизация (33 Мгц), тот же сигнал, что и CLK на шине PCI;

Дополнительные сигналы интерфейса LPC:

? LDRQ# — кодированный запрос DMA/Bus Master от периферии;

? SERIRQ — линия запросов прерывания (в последовательном коде), используется, если нет стандартных линий запросов IRQ в стиле ISA;

? CLKRUN# — сигнал, используемый для указания на остановку шины (в мобильных системах), требуется только для устройств, нуждающихся в DMA/BusMaster в системах, способных останавливать шину PCI;

? РМЕ# — событие системы управления потреблением (Power Management Event), может вводиться периферией, как и в PCI;

? LPCPD# — Power Down, указание от хоста устройствам на подготовку к выключению питания;

? LSMI# — запрос прерывания SMI# для повтора инструкции ввода-вывода.

Сигналы LFRAME# и LAD[3:0] синхронизированы (являются действительными) по фронту LCLK. По шине LAD[3:0] в каждом такте цикла передаются поля элементов протокола. Обобщенная временная диаграмма цикла обмена по LPC приведена на рис. 6.15. Начало каждого цикла хост отмечает сигналом LFRAME#, помещая на шину LAD[3:0] поле START. По сигналу LFRAME# все ПУ должны прекратить управление шиной LAD[3:0], а по коду поля START они должны декодировать последующие события как цикл шины. В следующем такте хост снимет сигнал LFRAME# и поместит на шину LAD[3:0] код типа цикла CYCTYPE. Сигнал LFRAME# может длиться и более одного такта, но признаком начала цикла (поля START) является последний такт перед снятием сигнала. С помощью сигнала LFRAME# хост может принудительно прервать цикл (например, по ошибке тайм-аута), выставив соответствующий код.

Рис. 6.15. Протокол LPC

В поле START возможны следующие коды:

? 0000 — начало цикла обращения хоста к устройству;

? 0010 — предоставление доступа ведущему устройству 0;

? 0011 — предоставление доступа ведущему устройству 1;

? 1111 — принудительное завершение цикла (abort).

Остальные коды зарезервированы.

Поле CYCTYPE задает тип и направление передачи. Бит 0 задает направление (0 — чтение, 1 — запись), биты [2:1] — тип обращения (00 — порт, 01 — память, 10 — DMA, 11 — резерв), бит 3 — резерв (0).

Поле TAR (Turn-Around) служит для смены «владельца» шины LAD[3:0], оно занимает 2 такта. В первом такте прежний владелец помещает код 1111, во втором переводит буферы в третье состояние.

Поле ADDR служит для передачи адреса. В цикле памяти оно занимает 8 тактов (32 бита), в цикле ввода-вывода — 4 такта. Передача адреса начинается со старших битов (чтобы раньше срабатывал дешифратор адреса).

В поле DATA передаются данные. На каждый байт требуется 2 такта, передача начинается с младшей тетрады. Многобайтные передачи начинаются с младшего байта.

Поле SYNC служит для введения тактов ожидания устройством, к которому выполняется обращение. Оно может содержать следующие коды (остальные зарезервированы):

? 0000 — готовность (без ошибок), для DMA означает снятие запроса для данного канала;

? 0101 — короткое ожидание (несколько тактов);

? 0110 — длинное ожидание;

? 1001 — готовность и присутствие запроса для канала DMA (для других типов обращения недопустимо);

? 1010 — ошибка: данные переданы, но возникли условия, при которых на шинах PCI или ISA выработался бы сигнал SERR# или IOCHK# (для DMA также означает снятие сигнала запроса).

Поле синхронизации обеспечивает контроль передачи, введение тактов ожидания и механизм тайм-аутов. Начав цикл, хост читает поле синхронизации. Если в течение трех тактов адресованное устройство не ответит, хост считает, что его нет на шине, и прекращает транзакцию. Если приходит код короткого ожидания, хост дожидается его смены на готовность или ошибку, но после 8 тактов ожидания он прервет транзакцию по тайм-ауту. Код длинного ожидания может приходить сколь угодно долго, ответственность за отсутствие зависания ложится на адресованное устройство. При прямом управлении поле SYNC выставляется хостом, и устройство должно терпеливо ожидать готовности, без каких-либо тайм-аутов. В самом быстром варианте (без тактов ожидания) поле SYNC занимает один такт.

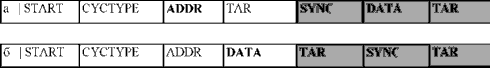

На рис. 6.16 приведена последовательность полей при обращениях хоста к памяти или портам (серым цветом помечены поля, вводимые устройством). Во всех этих обращениях передается по одному байту. Для чтения памяти, предполагая 5 тактов поля SYNC (время доступа к EPROM 120 нс), требуется 21 такт (0,63 мкс), что обеспечивает скорость чтения памяти 1,59 Мбайт/с. Если память конвейеризирована, то последующие обращения будут быстрее. Для записи в память поле SYNC займет 1 такт, а весь цикл — 17 тактов (0,51 мкс), что дает скорость записи 1,96 Мбайт/с. Обращения к портам за счет более короткой адресации и без тактов ожидания (1 такт SYNC) занимают по 13 тактов (0,39 мкс), что дает скорость 2,56 Мбайт/с для чтения и записи.

Рис. 6.16. Обращения к памяти и портам: а — чтение, б — запись

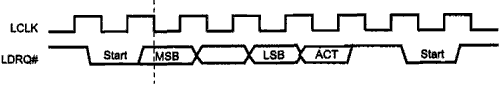

Для организации обмена по DMA и прямого управления хост должен иметь по одной входной линии LDRQ# для каждого подключенного устройства, использующего эти функции. По этой линии устройство передает состояние запросов каналов DMA в последовательном коде, как показано на рис. 6.17. Посылка начинается со старт-бита, за которой следуют код номера канала и бит запроса ACT: 1 (высокий уровень) — запрос активен, 0 — пассивен. Номер канала 4 (код 100) зарезервирован для прямого управления (он соответствует традиционно недоступному каналу DMA). Посылка передается при каждой смене состояния запросов. Нормально таким способом передается лишь запрос, а снятие его сигнализируется полем SYNC.

Рис. 6.17. Посылка запроса DMA или прямого управления

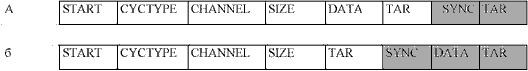

Передача данных DMA (рис. 6.18) выполняется под управлением хоста, но несколько отличается от обычных обращений к портам и памяти. Здесь появляются новые поля:

? поле SIZE определяет размер передачи: 0000 — 1 байт, 0001 — 2 байта, 0011 — 4 байта, остальные значения зарезервированы;

? поле CHANNEL служит для передачи хостом номера канала DMA (биты [2;0]) и признака конца цикла (TC, бит 3).

Рис. 6.18. Обращения DMA: а — чтение памяти, б — запись в память

Циклы чтения памяти, в зависимости от длины обращения (1, 2 или 4 байта), без тактов ожидания (они скрыты контроллером DMA) занимают 11, 18 и 32 тактов (0,33, 0,54 или 0,96 мкс), что обеспечивает производительность 3,03, 3,70 или 4,17 Мбайт/с соответственно. Циклы записи занимают 11,14 или 20 тактов (0,33, 0,42 или 0,60 мкс), что обеспечивает производительность 3,03, 4,76 или 6,67 Мбайт/с. На рисунке выделены рамкой последовательности полей, повторяющиеся при передаче 2 и 4 байтов.

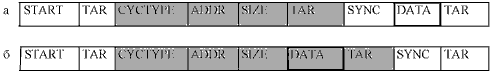

Прямое управление шиной ведущее устройство запрашивает так же, как и прямой доступ, но указывая зарезервированный номер канала 4 (100). Предоставляя управление, хост в поле START задает номер мастера, который позже определит тип цикла (рис. 6.19). Прямое управление подразумевает обращение к ресурсам хоста (системной памяти, устройству PCI). Данные в 2- и 4-байтных передачах следуют друг за другом без зазора, но в циклах чтения памяти и портов всегда будут такты ожидания, поскольку потребуется время на арбитраж шины PCI или доступ к контроллеру памяти. Из расчета 6 тактов (меньше — вряд ли, возможно и больше) поля SYNC, циклы обращения к памяти (и чтения, и записи) потребуют 25, 27 или 31 такт (0,75, 0,81 или 0,93 мкс), что обеспечивает производительность 1,33, 2,47 или 4,30 Мбайт/с. За счет более короткой адресации обращение к портам быстрее — 21, 23 или 27 тактов (0,63, 0,69 или 0,81 мкс), что обеспечивает производительность 1,59, 2,90 или 4,94 Мбайт/с.

Рис. 6.19. Обращения периферийного устройства (Bus Master): а — чтение памяти или порта, б — запись в память (порт)

Электрический интерфейс для сигналов LAD[3:0], LFRAME#, LDRQ# и SERIRQ соответствует спецификации PCI 2.1 для питания 3,3 В. Остальные сигналы в зависимости от системной платы могут быть с уровнями как 5 В, так и 3,3 В.

Конфигурирование устройств LPC не предусматривает использования протоколов PCI или ISA PnP, поскольку все устройства LPC априорно известны системной BIOS. Для обращения к устройствам LPC хост должен декодировать их адреса и направлять обращения по ним на контроллер LPC.

- 12. Лекция: Создание приложений с графическим интерфейсом пользователя.

- 5.21 IP-адреса, интерфейсы и множественное пребывание

- Множественные интерфейсы и имена методов

- 2.1 Интерфейс SCSI

- 2.2 Интерфейсы IDE, EIDE и АТА

- 7.2 Интерфейс WMI

- 7.5 Программные интерфейсы приложений для адаптеров шины

- Не допускайте того, чтобы поток пользовательского интерфейса блокировался на длительное время

- Абстрактные базы как двоичные интерфейсы

- Интерфейсы накопителей на жестких магнитных дисках

- Интерфейс SATA

- 8.4. Оформляем интерфейс проигрывателя