Книга: Аппаратные интерфейсы ПК. Энциклопедия

6.1.1. Обычная передача данных

6.1.1. Обычная передача данных

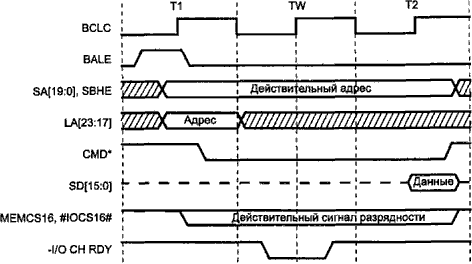

Для передачи данных от исполнителя к задатчику предназначены циклы чтения ячейки памяти или порта ввода-вывода, для передачи данных от задатчика к исполнителю — циклы записи ячейки памяти или порта ввода-вывода. В каждом цикле текущий (на время данного цикла) задатчик формирует адрес обращения и управляющие сигналы, а в циклах записи еще и данные на шине. Адресуемое устройство-исполнитель в соответствии с полученными управляющими сигналами принимает (в цикле записи) или формирует (в цикле чтения) данные. Также оно может, при необходимости, управлять длительностью цикла и разрядностью передачи. Обобщенные временные диаграммы циклов чтения или записи памяти или ввода-вывода приведены на рис. 6.2. Здесь условный сигнал CMD* изображает один из следующих сигналов:

? SMEMR#, MEMR# — в цикле чтения памяти;

? SMEMW#, MEMW# — в цикле записи памяти;

? IOR# — в цикле чтения порта ввода-вывода;

? IOW# — в цикле записи порта ввода-вывода.

Рис. 6.2. Временные диаграммы циклов чтения или записи на шине ISA

В каждом из рассматриваемых циклов активными (с низким уровнем) могут быть только сигналы лишь из одной строки данного списка, и во время всего цикла сигнал AEN имеет низкий уровень. Цикл прямого доступа к памяти, в котором это правило не соблюдается, рассмотрен ниже, и в таком цикле сигнал AEN будет иметь высокий уровень. Сигналы SMEMR# и SMEMW# вырабатываются из сигналов MEMR# и MEMW# соответственно, когда адрес принадлежит диапазону 0-FFFFFh. Поэтому сигналы SMEMR# и SMEMW# задержаны относительно MEMR# и MEMW# на 5-10 нс.

В начале каждого цикла контроллер шины устанавливает адрес обращения: на линиях SA[19:0] и SBHE# действительный адрес сохраняется на время всего текущего цикла; на линиях LA[23:17] адрес действителен только в начале цикла, так что требуется его «защелкивание». Каждое устройство имеет дешифратор адреса — комбинационную схему, срабатывающую только тогда, когда на шине присутствует адрес, относящийся к данному устройству. В фазе адресации устройства еще «не знают», к какому из пространств (памяти или ввода-вывода) относится выставленный адрес. Но дешифраторы адресов уже срабатывают, и, когда в следующей фазе шина управления сообщает тип операции, адресуемое устройство уже оказывается готовым к ее исполнению. Если устройство использует линии LA[23:17] (они нужны лишь для обращений к памяти выше границы FFFFFh), то они на дешифратор адреса должны проходить через регистр-защелку, «прозрачный» во время действия сигнала BALE и фиксирующий состояние выходов по его спаду. Это позволяет дешифратору, всегда вносящему некоторую задержку, начинать работу раньше, чем поступит управляющий сигнал чтения или записи. При обращении к портам ввода-вывода сигналы LA[32:17] не используются.

Если устройство имеет более одного регистра (ячейки), то для выбора конкретного регистра (ячейки) ему требуется несколько линий адреса. Как правило, старшие биты шины адреса поступают на вход дешифраторов адреса, формирующих сигналы выборки устройств, а младшие биты — на адресные входы самих устройств. Тогда каждое устройство в пространстве будет занимать наиболее компактную область смежных адресов размером в 2n байт, где n — номер младшей линии адреса, поступающей на дешифратор. Из них реально необходимы 2m адресов, где m — номер самой старшей линии адреса, участвующей в выборе регистра устройства. В идеале должно быть n=m+1: при большем значении n отведенное (по дешифратору) пространство адресов не будет использовано полностью и регистры устройства будут повторяться в отведенной области 2n-m-1 раз, то есть у них появятся адреса-псевдонимы (alias). Адреса-псевдонимы будут отличаться от истинного адреса (минимального из всех псевдонимов) на K?2m+1, где K — целое число. Меньшее значение n недопустимо, поскольку тогда не все регистры устройства будут доступны задатчику. В принципе можно использовать дешифратор адреса, срабатывающий только на какой-то части адресов из области 2n (не кратной степени двойки), если устройству требуется «неудобное» количество регистров. Однако на практике «фигурное выпиливание» областей из пространства адресов обычно не делают, так что часть адресов может пропадать бесполезно.

Разрядность данных в каждом цикле обращения определяется потребностями текущего задатчика и возможностями исполнителя. В IBM PC/XT и системная шина, и шина ISA были 8-разрядными, так что вопросов согласования разрядности не возникало. В IBM PC/AT286 (и 386-SX) системная шина уже 16-разрядная, и в современных ПК с 32- и 64-разрядными системными шинами контроллер шины ISA является ее 16-разрядным задатчиком. На системной плате имеется «косой буфер», он же перестановщик байтов, который при необходимости транслирует данные с младшего байта шины на старшую или обратно. Логика управления этим буфером использует сигналы SBHE#, SA0, IOCS16# и MEMCS16#. Поддержка 16-разрядных передач сообщается адресуемым исполнителем сигналами IOCS16# и MEMCS16# при срабатывании его дешифратора адреса. Сигнал IOCS16# влияет только на разрядность обращений к портам, MEMCS16# — к памяти. Все операции обмена (транзакции) начинаются задатчиком единообразно, поскольку он еще не «знает» возможностей исполнителя. Развитие событий зависит от намерений задатчика и полученных сигналов разрешения 16-битных передач. В чисто 16-разрядных машинах начальный адрес однозначно соответствует передаваемому байту или младшему байту передаваемого слова[3]. В машинах с 32-разрядными процессорами начальный адрес, выставляемый на шине в начале транзакции, зависит от разрядности данных, запланированной задатчиком, и может зависеть от положения адресуемых данных относительно границы двойного слова (32 битного). 16-разрядные передачи выполняются за 1 цикл только при условии передачи по четному адресу (A0=0) и при ответе исполнителя сигналом IOCS16# или MEMCS16#, в иных случаях они разбиваются на два цикла. 32-разрядные передачи будут разбиваться на 2 (16+16), 3 (8+16+8) или 4 (8+8+8+8) цикла, в зависимости от возможностей исполнителя и четности адреса. Порядок, в котором передаются байты (во времени), неоднозначен (возможен как инкремент, так и декремент адреса), но в адресном пространстве они раскладываются по своим местам однозначно.

В табл. 6.4 приводятся состояния сигналов шины ISA для различных вариантов записи в порты ввода-вывода, проверенные экспериментальным путем. Вывод 16-разрядных данных выполнялся командой OUT DX, AX (в DX — адрес порта, в АХ — данные; AL содержит младший байт, АН — старший), вывод 8-разрядных — командой OUT DX, AL. Несколько неожиданные (для автора) варианты 3 и 6 с декрементом адреса, возможно, будут иметь место не на всех системных платах, но их следует иметь в виду при проектировании устройств, претендующих на глобальную совместимость. Правда на практике 16-битных передач по нечетным адресам обычно избегают (даже чисто подсознательно), и побочные эффекты от такого порядка маловероятны.

Таблица 6.4. Состояние сигналов при 8- и 16-битных обращениях к устройству ISA

| Сигнал (шина) | 1 цикл | 2 цикл |

|---|---|---|

| 1. Вывод 16-разрядных данных в 16-битное устройство по четному адресу | ||

| SBHE# | L | - |

| SA | DX(A0=0) | - |

| D[15:8] | АН | - |

| D[7:0] | AL | - |

| IOCS16# | L | - |

| 2. Вывод 16-разрядных данных в 16-битное устройство по нечетному адресу ххх1, ххх5, xxx9, xxxD | ||

| SBHE# | L | H |

| SA | DX(A0=1) | DX+1 (A0=0) |

| D[15:8] | AL | 0 |

| D[7:0] | AL | AH |

| IOCS16# | L | L |

| 3. Вывод 16-разрядных данных в 16-битное устройство | ||

| SBHE# | H | L |

| SA | DX+1 (A0=0) | DX (A0=1) |

| D[15:8] | 0 | AL |

| D[7:0] | AH | 0 |

| IOCS16# | L | L |

| 4. Вывод 16-разрядных данных в 8-битное устройство по четному адресу | ||

| SBHE# | L | L |

| SA[1:0] | DX(A0=0) | DX+1 (A0=1) |

| D[15:8] | AH | AH |

| D[7:0] | AL | AH |

| IOCS16# | H | H |

| 5. Вывод 16-разрядных данных в 8-битное устройство по нечетному адресу ххх1, ххх5, xxx9, xxxD | ||

| SBHE# | L | H |

| SA[1:0] | DX(A0=1) | DX+1 (A0=0) |

| D[15:8] | AL | 0 |

| D[7:0] | AL | AH |

| IOCS16# | H | H |

| 6. Вывод 16-разрядных данных в 8-битное устройство по нечетному адресу xxx3, ххх7, xxxB, xxxF | ||

| SBHE# | H | L |

| SA[1:0] | DX+1(A0=0) | DX(A0=1) |

| D[15:8] | 0 | AL |

| D[7:0] | AH | AL |

| IOCS16# | H | H |

| 7. Вывод 8-разрядных данных в 16-битное устройство по четному адресу | ||

| SBHE# | H | - |

| SA[1:0] | DX(A0=0) | - |

| D[15:8] | 0 | - |

| D[7:0] | AL | - |

| IOCS16# | L | - |

| 8. Вывод 8-разрядных данных в 16-битное устройство по нечетному адресу | ||

| SBHE# | L | - |

| SA[1:0] | DX(A0=1) | - |

| D[15:8] | AL | - |

| D[7:0] | 0(AL?) | - |

| IOCS16# | L | - |

Момент помещения действительных данных на линии SD[15:0] определяется управляющими сигналами чтения/записи, так что исполнителю не требуется синхронизация с тактовым сигналом шины. В циклах чтения адресованный исполнитель должен выдать данные на шину по началу (спаду) соответствующего сигнала чтения (IOR#, MEMR#, SMEMR#) и удерживать их до конца действия сигнала (пока не произойдет подъем сигнала). В циклах записи задатчик выставляет действительные данные несколько позже начала (спада) сигнала записи (IOW#, MEMW#, SMEMW#). Устройство-исполнитель должно фиксировать для себя эти данные в конце цикла по подъему сигнала записи. От устройства-исполнителя не предусматривается никаких подтверждений исполнения циклов; длительность цикла устанавливает задатчик, но исполнитель может потребовать удлинения или укорочения циклов. С помощью сигнала IOCHRDY исполнитель может удлинить цикл на произвольное число тактов, при этом задатчик будет вводить дополнительные такты ожидания (wait states). Обычно контроллер шины следит за длительностью цикла и по достижении критического времени принудительно его завершает (по тайм-ауту, возможно, и не сообщая об этом событии). Слишком длинные циклы тормозят работу компьютера, а превышение длительности 15 мкс может привести к сбою регенерации и потере данных в ОЗУ. С помощью сигнала 0W# исполнитель предлагает задатчику укоротить цикл, исключив такты ожидания. Реакция задатчика на одновременное использование сигналов IOCHRDY и 0WS# непредсказуема, этой ситуации следует избегать.

ВНИМАНИЕ

Некорректное управление сигналом IOCHRDY (его «залипание» на низком уровне) тормозит работу компьютера.

Номинальная длительность цикла определяется чипсетом и может программироваться в BIOS Setup заданием числа тактов ожидания (wait states). При этом циклы обращения к памяти, как правило, короче циклов обращения к портам ввода-вывода. Для управления длительностью цикла используются также сигналы управления разрядностью передачи: если устройство поддерживает 16-битные передачи, предполагается, что оно может работать с меньшим количеством тактов ожидания. Этим объясняется, что в BIOS Setup длительности циклов ISA задаются раздельно как для памяти и ввода-вывода, так и для 8- и 16-битных операций.

Кроме длительности цикла, устройства могут быть критичны к времени восстановления (recovery time) — длительности пассивного состояния управляющих сигналов чтения-записи между циклами. Этот параметр также может программироваться в BIOS Setup и тоже раздельно для 8- и 16-разрядных операций.

Карты расширения для подключения к шине данных, как правило, используют буферные микросхемы, раздельные для линий SD[7:0] и SD[15:8]. Здесь широко применяются микросхемы 74ALS245 (1533АП6) — 8-разрядные двунаправленные приемопередатчики. Буфер должен открываться сигналом ОЕ# (Output Enable — разрешение выхода), когда на шине адреса присутствует адрес, относящийся к диапазону адресов подключаемого устройства. «Дежурным» является направление передачи «от шины — к устройству»; переключение в обратную сторону производится по сигналу IOR#, если устройство представляет порты ввода-вывода, или MEMRD#, если устройство приписано к пространству памяти. Таким образом, буферы имеют право передавать данные на шину (управлять шиной данных) только во время действия сигнала чтения, относящегося к зоне адресов данного устройства. Карта расширения может являться комбинацией 8- и 16-битных устройств; например, некогда популярные мультикарты содержали 16-битный адаптер ATA и набор 8-битных контроллеров портов COM, LPT, GAME и контроллера НГМД. В таких картах логика управления буферами и сигналами IOCS16# и MSC16# управляется сигналами от дешифратора адреса. Если устройство по данному адресу является 8-разрядным (не формирует сигналы IOCS16# или MSC16#), то оно имеет право разрешать чтение только через буфер линий SD[7:0], а буфер старших линий SD[15:8] (если он имеется на карте) должен быть переведен в третье состояние. Если устройство по данному адресу является 16-разрядным, то оно формирует сигнал IOCS16# или MSC16#, а разрешением буферов управляют сигналы SBHE# и SA0. В этом случае буфер линий SD[7:0] разрешается только при SA0=0, а буфер линий SD[15:8] разрешается только при SBHE#=L. Некорректное разрешение буферов может приводить к их конфликту с перестановщиком байтов системной платы и искажениям данных.

Восьмиразрядные устройства (например, микросхемы 8255, 8250, 8253 и т. п.) следует подключать только к линиям SD[7:0] и при обращении к ним не формировать сигналы IOCS16# или MSC16#. Никакие «косые» буферы (перестановщики байтов) на интерфейсных картах не нужны.

В одном из источников описывается эффект перестановки байтов при обращении к порту ввода-вывода: «Если прочитать слово из порта по четному адресу, значение одно, а если по нечетному — старшие 8 бит предыдущего значения становятся младшими, а старшие нового = FFh». Первые подозрения падают на ошибку в логике управления буферами. На самом деле все объясняется гораздо проще. Пусть имеется устройство с двухбайтным регистром, младший байт которого имеет адрес R0 (четный), старший — R0+1, а по адресу R+2 устройство (и никакие другие) не откликается. Пусть в данный момент в нем записано число AA55h, тогда чтением порта по команде IN AX, R0 получим в регистрах процессора AL=55h, AH=AAh. Теперь если попытаться его «прочитать по нечетному адресу», то есть командой IN АХ, R0+1, то получим AL=AAh (содержимое R0+1, к которому мы на самом деле и адресовались!), a AH=FFh (результат чтения «пустоты»). Так что это не «эффект перестановки», а просто незнание общего правила «интеловской» адресации: адресом слова (двойного, учетверенного…) является адрес его младшего байта. Если в нашем устройстве применяется неполная дешифрация адреса (линия SA1 не используется ни для дешифрации адреса, ни для выбора регистра), то мы увидим полную перестановку байт — в AH=55h, результат чтения R0 по адресу-псевдониму R0+2. Логика работы контроллера шины вместе со всеми буферами делает обращение к любой ячейке памяти или порту инвариантным к способу программной адресации — что закажешь, то и получишь, но требуется учитывать особенности периферийных устройств, у которых в адресации портов нередко встречаются псевдонимы. Адреса-псевдонимы встречаются и в пространстве памяти (например, копии образов BIOS под границей 1-го и 16-го мегабайтами памяти в «классических» PC/AT).

- Передача данных

- Обычная криптография

- Резервное копирование базы данных InterBase

- Firebird РУКОВОДСТВО РАЗРАБОТЧИКА БАЗ ДАННЫХ

- Резервное копирование многофайловых баз данных

- Восстановление из резервных копий многофайловых баз данных

- Владелец базы данных

- ЧАСТЬ IV. База данных и ее объекты.

- Перевод базы данных InterBase 6.x на 3-й диалект

- Типы данных для работы с датой и временем

- Практическая работа 53. Запуск Access. Работа с объектами базы данных

- Обзор основных причин повреждения базы данных