Книга: Distributed operating systems

6.3.4. PRAM Consistency and Processor Consistency

6.3.4. PRAM Consistency and Processor Consistency

In causal consistency, it is permitted that concurrent writes be seen in a different order on different machines, although causally-related ones must be seen in the same order by all machines. The next step in relaxing memory is to drop the latter requirement. Doing so gives PRAM consistency (Pipelined RAM), which is subject to the condition:

Writes done by a single process are received by all other processes inthe order in which they were issued, but writes from different processes may be seen in a different order by different processes.

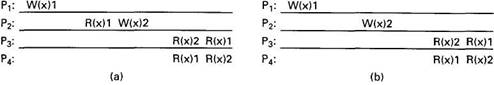

Fig. 6-17. (a) A violation of causal memory. (b) A correct sequence of events in causal memory.

PRAM consistency is due to Lipton and Sandberg (1988). PRAM stands for Pipelined RAM, because writes by a single process can be pipelined, that is, the process does not have to stall waiting for each one to complete before starting the next one. PRAM consistency is contrasted with causal consistency in Fig. 6-18. The sequence of events shown here is allowed with PRAM consistent memory but not with any of the stronger models we have studied so far.

Fig. 6-18. A valid sequence of events for PRAM consistency.

PRAM consistency is interesting because it is easy to implement. In effect it says that there are no guarantees about the order in which different processes see writes, except that two or more writes from a single source must arrive in order, as though they were in a pipeline. Put in other terms, in this model all writes generated by different processes are concurrent.

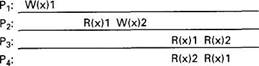

Let us now reconsider the three processes of Fig. 6-14, but this time using PRAM consistency instead of sequential consistency. Under PRAM consistency, different processes may see the statements executed in a different order. For example, Fig. 6-19(a) shows how P1 might see the events, whereas Fig. 6-19(b) shows how P2 might see them and Fig. 6-19(c) shows P3's view. For a sequentially consistent memory, three different views would not be allowed.

| a = 1; | a = 1; | b = 1; |

| * print(b, c); | b = 1; | print(a, c); |

| b = 1; | * print (a, c); | c = 1; |

| print(a, c); | print(b, c); | * print(a, b); |

| c = 1; | c = 1; | a = 1; |

| print(a, b); | print(a, b); | print(b, c); |

| Prints: 00 | Prints: 10 | Prints: 01 |

| (a) | (b) | (с) |

Fig. 6-19. Statement execution as seen by three processes. The statements marked with asterisks are the ones that actually generate output.

If we concatenate the output of the three processes, we get a result of 001001, which, as we saw earlier, is impossible with sequential consistency. The key difference between sequential consistency and PRAM consistency is that with the former, although the order of statement execution (and memory references) is nondeterministic, at least all processes agree what it is. With the latter, they do not agree. Different processes can see the operations in a different order.

Sometimes PRAM consistency can lead to results that may be counterintuitive. The following example, due to Goodman (1989), was devised for a slightly different memory model (discussed below), but also holds for PRAM consistency. In Fig. 6-20 one might naively expect one of three possible outcomes: P1 is killed, P2 is killed, or neither is killed (if the two assignments go first). With PRAM consistency, however, both processes can be killed. This result can occur if P1 reads b before it sees P2's store into b, and P2 reads a before it sees P1's store into a. With a sequentially consistent memory, there are six possible statement interleavings, and none of them results in both processes being killed.

| a = 1; | b = 1; |

| if (b == 0) kill (P2); | if (a == 0) kill (P1); |

| (a) | (b) |

Fig. 6-20. Two parallel processes. (a)P1 (b)P2.

Goodman's (1989) model, called processor consistency, is close enough to pram consistency that some authors have regarded them as being effectively the same (e.g., Attiya and Friedman, 1992; and Bitar, 1990). However, Goodman gave an example that suggests he intended that there be an additional condition imposed on processor consistent memory, namely memory coherence, as described above: in other words, for every memory location, x, there be global agreement about the order of writes to x. Writes to different locations need not be viewed in the same order by different processes. Gharachorloo et al. (1990) describe using processor consistency in the Dash multiprocessor, but use a slightly different definition than Goodman. The differences between PRAM and the two processor consistency models are subtle, and are discussed by Ahamad et al. (1993).

- 6.3. CONSISTENCY MODELS

- Разработка приложений баз данных InterBase на Borland Delphi

- Open Source Insight and Discussion

- Introduction to Microprocessors and Microcontrollers

- Chapter 6. Traversing of tables and chains

- Chapter 8. Saving and restoring large rule-sets

- Chapter 11. Iptables targets and jumps

- Chapter 5 Installing and Configuring VirtualCenter 2.0

- Chapter 16. Commercial products based on Linux, iptables and netfilter

- Appendix A. Detailed explanations of special commands

- Appendix B. Common problems and questions

- Appendix E. Other resources and links