Книга: Аппаратные интерфейсы ПК. Энциклопедия

11.4. Интерфейс JTAG

11.4. Интерфейс JTAG

Интерфейс JTAG (Joint Test Action Group) предназначен для тестирования сложных логических схем, установленных в целевое устройство. Этот интерфейс описан в стандарте IEEE 1149.1 Boundary Scan Architecture и является последовательным синхронным, но в связи со спецификой назначения значительно отличается от вышеописанных интерфейсов, ориентированных на передачу данных. Интерфейсом JTAG управляет одно устройство-контроллер (чаще всего это ПК с соответствующим интерфейсным адаптером), к которому может быть подключено несколько тестируемых устройств. Ниже перечислены сигналы интерфейса JTAG.

? TCK (Test Clock) — сигнал синхронизации последовательных данных; генерируется контроллером. Частота синхронизации может достигать 16 МГц.

? TMS (Test Mode Select) — сигнал выбора тестового режима. Генерируется контроллером.

? TDI (Test Data Input) — входные данные, принимаемые устройством в последовательном двоичном коде (младшим битом вперед).

? TDO (Test Data Output) — выходные данные, передаваемые устройством в последовательном двоичном коде.

? TRST (Test Logic Reset) — необязательный сигнал сброса логики интерфейсного порта, генерируемый контроллером.

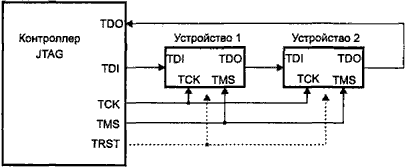

Эти сигналы (все однонаправленные), имеющие обычные логические уровни, образуют тестовый порт TAP (Test Access Port), через который тестируемое устройство подключается к тестирующему оборудованию (контроллеру). В задачу тестирующего оборудования входит формирование тестовых сигналов по программе тестирования, определенной разработчиком тестируемого устройства, и сравнение полученных результатов с эталонами. Один и тот же контроллер и порт могут использоваться для тестирования любого числа устройств, поддерживающих JTAG. Для этого устройства своими портами TAP соединяются в цепочку (рис. 11.6). Стандартизованный логический формат позволяет контроллеру независимо общаться с каждым из устройств цепочки (для этого, конечно, они должны иметь исправные ячейки JTAG).

Рис. 11.6. Цепочка устройств с интерфейсом JTAG

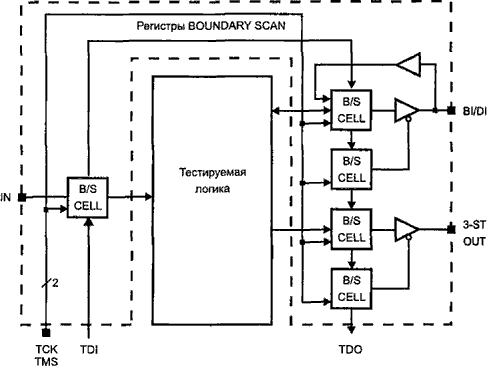

Идею тестирования любой цифровой схемы иллюстрирует рис. 11.7, на котором показана условная цифровая система, имеющая входные, выходные (возможно, с третьим состоянием) и двунаправленные сигналы. Ячейки тестирования B/S врезаются между реальными внешними выводами устройства и собственно логическим устройством, то есть располагаются на логической границе (boundary) устройства. TAP-контроллер способен сканировать ячейки — управлять ими и считывать с них информацию. Отсюда и пошло название Boundary Scan, которое можно перевести как «периферийное сканирование». При включенном тестовом режиме TAP-контроллер может логически отсоединить сигналы от внешних выводов, задавать входные воздействия и считывать результаты — собственно, это все, что необходимо для тестирования последовательностных схем (автоматов с памятью). Прелесть JTAG заключается в том, что независимо от сложности устройства оно тестируется с помощью всего лишь четырех сигналов — все сложности прячутся в достаточно простые ячейки, «окутывающие» его сигнальные выводы.

Рис. 11.7. Включение ячеек сканирования

Тестовая логика, встраиваемая в устройство, поддерживающее JTAG, состоит из следующих элементов:

? тестовый порт TAP (четыре интерфейсных сигнала);

? TAP-контроллер, управляющий тестовыми регистрами;

? регистр инструкций IR (Instruction Register), который принимает последовательный код со входа TDI (код инструкции используется для выбора исполняемой тестовой операции или регистра тестовых данных, к которым производится обращение);

? регистры тестовых данных, из которых любое устройство должно иметь три обязательных регистра: ВPR (Bypass Register), DID (Device Identification Register) и BSR (Boundary Scan Register).

Регистры инструкций и данных представляют собой независимые сдвиговые регистры, соединенные параллельно. На их входы (старшие биты) приходит сигнал TDI, с выходов (младшие биты) снимается сигнал TDO. По каждому положительному перепаду данные продвигаются на один бит.

Регистр ВРR имеет длину в один бит. Он используется как кратчайший обходной путь для последовательных данных, когда остальные регистры не участвуют в обмене.

Регистр BSR представляет собой длинный сдвигающий регистр, каждым битом которого являются пограничные ячейки, установленные на всех входных и выходных сигналах процессора. Для двунаправленных сигналов (или их групп), кроме собственно информационных ячеек регистра, соответствующих внешним сигналам, имеются и управляющие ячейки, задающие режим работы информационных ячеек. К примеру, у процессоров P6 длина BSR составляет 159 бит.

Регистр DID длиной 32 бита содержит идентификатор производителя, код устройства и номер версии, по которым TAP-контроллер может распознать, с каким устройством он имеет дело.

Регистр IR служит для хранения исполняемой тестовой инструкции. Его длина зависит от тестируемого устройства. Для всех устройств обязательными являются инструкции BYPASS, IDCODE, SAMPLE и EXTEST.

Инструкция BYPASS (все биты кода — единичные) предназначена для подключения однобитного обходного регистра, обеспечивая скорейшее прохождение данных через устройство; при этом оно никак не реагирует на проходящий поток. Вход TDI обычно «подтягивают» резистором к высокому уровню, при этом разрыв цепочки JTAG приведет к подключению обходных регистров во всех устройствах после точки обрыва. Это исключает возможные непредсказуемые действия устройств в случае обрыва.

Инструкция идентификации IDCODE (младшие биты кода — 10) подключает к интерфейсу регистр DID, позволяя считать его содержимое (поступающие входные данные не могут изменить его значение).

Инструкция SAMPLE/PRELOAD (младшие биты кода — 01) имеет два назначения. Когда TAP-контроллер находится в состоянии Capture-DR (см. ниже), эта инструкция позволяет выполнить моментальный «снимок» состояния всех внешних сигналов без воздействия на работу устройства. Значение сигналов фиксируется по положительному перепаду TCK. В состоянии Update-DR по этой инструкции данные загружаются в выходные ячейки тестового порта (но еще не на выходы устройства), откуда впоследствии они будут выводиться (подаваться на выводы процессора) по инструкции EXTEST. Данные загружаются по спаду сигнала TCK.

Инструкция EXTEST (младшие биты кода — 00) предназначена для проверки внешних цепей (по отношению к тестируемому устройству). При этом на выходные выводы подаются сигналы, предварительно записанные в регистр BSR, а состояние входных сигналов фиксируется в этих регистрах. Двунаправленные сигналы предварительно конфигурируются соответствующими им управляющими битами ячеек BSR.

Стандарт 1149.1 предусматривает и инструкцию тестирования внутренней логики устройства INTEST, но ее поддерживают не все устройства.

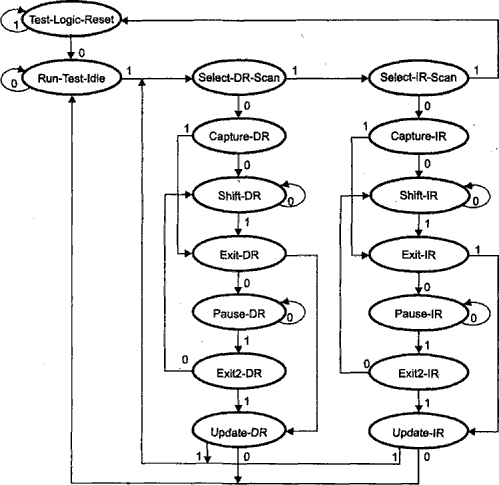

Контроллер тестового порта (TAP-controller) представляет собой синхронный конечный автомат, изменяющий состояние по фронту сигнала TCK и по включению питания. Сменой состояний управляет сигнал TMS (Test Mode State), воспринимаемый по положительному перепаду TCK. Граф состояний и переходов управляющего автомата представлен на рис. 11.8. Около стрелок переходов указаны значения сигнала TMS во время фронта TCK.

Рис. 11.8. Граф состояний и переходов контроллера TAP

В исходное состояние Test-Logic-Reset контроллер автоматически переходит по включении питания и из любого другого состояния может быть переведен высоким уровнем TMS, удерживаемым не менее пяти тактов TCK. Для перевода в состояние Test-Logic-Reset иногда используют и дополнительный сигнал TRST. В этом состоянии тестовая логика запрещена, и устройство работает в нормальном режиме.

Состояние Run-Test/Idle является промежуточным между выполнением тестовых операций. В этом состоянии регистры не изменяют своего значения.

В состоянии Capture-DR во время выполнения инструкций EXTEST и SAMPLE/PRELOAD сканирующий регистр фиксирует только данные на входных линиях.

В состоянии Shift-DR данные с TDI продвигаются через подключенный сдвиговый регистр на выход TDO.

В состоянии Pause-DR контроллер временно запрещает продвижение данных через сдвиговый регистр.

В состоянии Update-DR по спаду TCK сигналы из сдвигового регистра фиксируются на выходах тестовых ячеек.

В состоянии Capture-IR контроллер загружает в сдвиговый регистр инструкций код «безобидной» инструкции SAMPLE.

В состоянии Shift-IR в цепь между TDI и TDO включается сдвиговый регистр инструкций, но еще исполняется предыдущая инструкция.

В состоянии Pause-IR контроллер временно запрещает продвижение данных через сдвиговый регистр инструкций.

В состоянии Update-IR по спаду TCK фиксируется новая исполняемая инструкция, и в цепь TDI-TDO включается соответствующий ей регистр.

Кроме этих основных состояний контроллера, определяющих действия тестового оборудования, имеются и временные промежуточные состояния, необходимые для реализации переходов автомата. К ним относятся Select-DR-Scan, Exit1-DR, Exit2-DR, Select-DR-Scan, Exit1-IR и Exit2-IR.

Для интерфейса JTAG существует специальный язык описания устройств BSDL (Boundary Scan Description Language). Состав и порядок следования информационных и управляющих ячеек в сдвиговом регистре данных специфичен для каждого устройства (для чего и существует идентификационный регистр) и сообщается его разработчиками.

Интерфейс JTAG используется не только для тестирования, но и для программирования различных устройств, в том числе и энергонезависимой памяти микроконтроллеров. Контакты для сигналов JTAG имеются на шине PCI, однако в их использовании единообразия не наблюдается (либо остаются неподключенными, либо соединяются для организации цепочки). Интерфейс JTAG имеется в современных процессорах; здесь он позволяет не только тестировать сам процессор (это не представляет особого прикладного интереса), но и организовать зондовый режим отладки (probe mode, см. [6, 7]). Зондовый режим является мощным средством отладки системного программного обеспечения; обычный процессор, связанный с тестовым контроллером интерфейсом JTAG, превращается во внутрисхемный эмулятор — мечту разработчика системного ПО.

- Глава 11 Вспомогательные последовательные интерфейсы и шины

- 11.5. Программно-управляемая реализация последовательных интерфейсов

- 12. Лекция: Создание приложений с графическим интерфейсом пользователя.

- 5.21 IP-адреса, интерфейсы и множественное пребывание

- Множественные интерфейсы и имена методов

- 2.1 Интерфейс SCSI

- 2.2 Интерфейсы IDE, EIDE и АТА

- 7.2 Интерфейс WMI

- 7.5 Программные интерфейсы приложений для адаптеров шины

- Не допускайте того, чтобы поток пользовательского интерфейса блокировался на длительное время

- Абстрактные базы как двоичные интерфейсы

- Интерфейсы накопителей на жестких магнитных дисках