Книга: Аппаратные интерфейсы ПК. Энциклопедия

11.2. Шина управления SMI интерфейса MII

11.2. Шина управления SMI интерфейса MII

В спецификации IEEE 802.3u сетевой технологии Ethernet от 1995 г. появился интерфейс MII (Media Independent Interface — интерфейс, независимый от среды передачи), позволяющий отделять специфические устройства физического уровня (PHY) от вышестоящих уровней. Кроме интерфейса передачи «полезных» данных сети в MII входит последовательный интерфейс SMI (Serial Management Interface), обеспечивающий доступ к внутренним регистрам PHY. Эти регистры позволяют отслеживать состояние PHY и управлять им; в частности, и управлять согласованием режимов сетевых портов. В спецификации описаны регистры, обязательные для устройств, а также отведено место для специфических регистров, используемых по воле разработчика. Интерфейс SMI представляет собой последовательную синхронную трехпроводную шину (сигналы MDC, MDIO и шина GND), обеспечивающую доступ по записи и чтению к 16-разрядным регистрам устройств. Протокол шины обеспечивает 5-битную адресацию подключаемых устройств, что позволяет непосредственно объединять до 32 устройств на одной шине. Каждое устройство может иметь до 32 регистров. Шина является хост-центрической — ею управляет один контроллер, инициирующий транзакции, а все подключаемые устройства являются ведомыми. Контроллер генерирует импульсы синхронизации по однонаправленной линии MDC, а по двунаправленной линии MDIO формирует биты команд и данных (при записи) и принимает данные чтения. Устройство, опознавшее свой адрес, должно выполнить адресуемую ему команду. Уровни сигналов — обычные для логики ТТЛ и КМОП; для линии MDIO обычно используются формирователи с открытым коллектором (стоком) и резисторы, «подтягивающие» пассивную линию к уровню питания (+5 или +3,3 В). Частота импульсов MDC, не обязательно постоянная, не должна превышать 2,5 МГц, что позволяет реализовать функции контроллера чисто программно. Временны??е диаграммы сигналов для транзакций чтения и записи приведены на рис. 11.4. Отметим, что устройство должно фиксировать биты по положительному перепаду MDC, а контроллер фиксирует биты по отрицательному перепаду. Адреса и данные передаются начиная со старших бит.

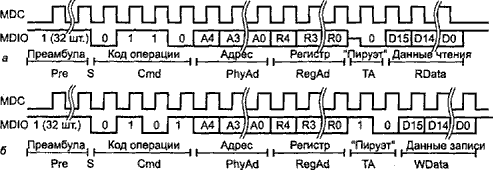

Рис. 11.4. Транзакции на шине SMI: a — запись, б — чтение

В общем случае каждой транзакции должна предшествовать преамбула Pre — не менее 32 тактов нахождения MDIO на высоком уровне. Собственно транзакция начинается с условия Start — вывода контроллером битовой последовательности «01», за которым следует двухбитная команда Cmd: «10» — чтение или «01» — запись. Далее контроллер передает 5-битный адрес устройства (PhyAd), за которым следует 5-битный номер регистра (RegAd). После этого следует двухбитный «пируэт» (turnaround) ТА для перехода к передаче данных. При операции записи «пируэт» сводится к передаче контроллером последовательности «10», а затем он передает 16 бит данных (WData) для записи в регистр. При чтении с начала «пируэта» контроллер отпускает линию MDIO, а на время второго бита отозвавшееся адресованное устройство устанавливает на этой линии нуль, что используется для определения факта ответа. В следующие 16 тактов устройство передает считанные данные (RData) контроллеру.

Преамбула нужна только для приведения интерфейсной части устройств в исходное состояние (после подачи питания); если питание устройством не терялось, то последующие транзакции могут выполняться и без преамбулы. Имеется также нюанс в «пируэте»: для некоторых устройств второй его бит оказывается лишним — он сбивает синхронизацию данных на 1 такт.

- Основные "рычаги" управления производительностью

- Категорийный менеджмент. Курс управления ассортиментом в рознице

- 1. Системы управления базами данных

- 4.8 Методы управления Fibre Channel

- 7.9 Будущее управления хранилищами по версии ассоциации SNIA: стандарты SMI

- 15.1.3. Обработка сигналов управления заданиями

- Группа управления конфигурацией ПО

- Не допускайте того, чтобы поток пользовательского интерфейса блокировался на длительное время

- Системные вызовы управления процессорной привязкой

- Глава 2 Комбинированная система управления

- Запуск сценариев на удаленных машинах. Контроль за ходом выполнения таких сценариев

- Почему я не нахожу в Панели управления описанных пунктов?