Книга: Аппаратные интерфейсы ПК. Энциклопедия

11.3. Интерфейс SPI

11.3. Интерфейс SPI

Интерфейс SPI (Serial Peripheral Interface), он же Microwire, — трехпроводный синхронный с раздельными линиями входных и выходных данных — применяется для связи микроконтроллеров с периферийными микросхемами и микросхемами памяти. С его помощью программируются многие микросхемы программируемой логики (например, FPGA фирмы Altera), применяемые в различных узлах ПК и периферии. По сравнению с I?C интерфейс SPI обеспечивает более высокую скорость передачи данных. Частота синхронизации может достигать 5 МГц (зависит от подключаемых устройств); при этом за каждый такт синхронизации одновременно может и передаваться, и приниматься очередной бит данных. В основном варианте использования предполагается, что интерфейс соединяет одно ведущее устройство с одним или несколькими ведомыми устройствами. Интерфейс может применяться и для обмена между несколькими микроконтроллерами, допуская наличие на шине нескольких ведущих устройств, но протокол предоставления доступа не стандартизован. Ниже рассматривается работа интерфейса с одним ведущим устройством. В интерфейсе используются 3 обязательных сигнала:

? SCK (Serial Clock) — синхросигнал, которым ведущее устройство стробирует каждый бит данных;

? MOSI (Master Output Slave Input) — выходные данные ведущего устройства и входные данные ведомого устройства;

? MISO (Master Input Slave Output) — входные данные ведущего устройства и выходные данные ведомого устройства.

Кроме того, может использоваться сигнал выбора ведомого устройства SS# (Slave Select, или CS# — Chip Select): ведомое устройство должно реагировать на сигналы интерфейса и генерировать выходные данные на линии MISO только при низком уровне этого сигнала; при высоком уровне выход MISO должен переводиться в высокоимпедансное состояние. С помощью сигналов SS#, раздельно формируемых ведущим устройством для каждого из ведомых устройств, ведущее устройство может выбирать партнером в транзакции одно из ведомых. При этом получается гибридная топология соединений: по сигналам SCK, MOSI и MISO — топология шинная, по SS# — звездообразная (центр — ведущее устройство).

Возможен и иной способ общения ведущего устройства с несколькими ведомыми устройствами с чисто шинной топологией. Здесь сигнал SS# для выбора устройств не используется, но ведомые устройства все время «слушают» шину, ожидая специальной адресной посылки в начале транзакции. Опознав свой адрес, устройство отрабатывает дальнейшие протокольные посылки, и теперь ему разрешается выводить данные на линию MISO до конца текущей транзакции. Однако этот вариант требует довольно сложной логики поведения ведомого устройства.

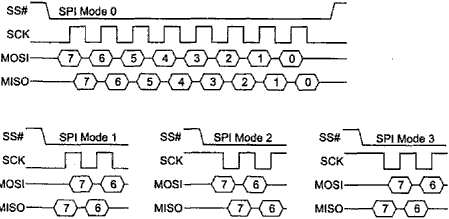

Данные передаются старшим битом вперед. Устройства различных производителей могут использовать разные режимы обмена (SPI Mode 0…SPI Mode 3), различающиеся фазой и полярностью синхросигналов. Рис. 11.5 иллюстрирует передачу и прием байта в различных режимах. Заметим, что в любом режиме входные и выходные данные стробируются по разным перепадам синхроимпульсов. Кроме того, есть варианты в использовании сигнала SS#. В первом варианте (он и представлен на рисунке) для ведомого устройства признаком начала транзакции является спад сигнала SS#, а завершения — его подъем. Во втором варианте начало транзакции определяется по первому фронту (спаду) SCK, а сигнал SS# может иметь низкий уровень постоянно. Второй вариант иногда предпочитают для простейшего двухточечного интерфейса с единственным ведущим устройством и единственным ведомым устройством, когда нет опасения потери синхронизации. Микроконтроллеры с аппаратным портом SPI, как правило, имеют возможность программного выбора режима. Форматы транзакций зависят от устройств, но общая идея такова: ведущее устройство по линии MOSI посылает код операции и адресную информацию для устройства; затем следуют данные. В операции записи они передаются ведущим устройством по той же линии, в операции чтения устройство их посылает по линии MISO. На время всей транзакции ведущее устройство сохраняет активное состояние линии SS#, число требуемых синхроимпульсов зависит от формата команды.

Рис. 11.5. Форматы передач по интерфейсу SPI

- 4.19. Синхронный последовательный интерфейс SPI

- 4.19.1 Концепция интерфейса SPIФункциональная схема обмена между двумя контроллерами SPI

- 4.19.5 Периферийные ИС с интерфейсом SPI

- 12. Лекция: Создание приложений с графическим интерфейсом пользователя.

- LOCK ACQUIRE SPINS

- 5.21 IP-адреса, интерфейсы и множественное пребывание

- Множественные интерфейсы и имена методов

- 2.1 Интерфейс SCSI

- 2.2 Интерфейсы IDE, EIDE и АТА

- 7.2 Интерфейс WMI

- 7.5 Программные интерфейсы приложений для адаптеров шины

- Не допускайте того, чтобы поток пользовательского интерфейса блокировался на длительное время