Книга: Real-Time Concepts for Embedded Systems

6.4.3 Credit-Tracking Synchronization

6.4.3 Credit-Tracking Synchronization

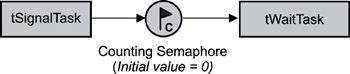

Sometimes the rate at which the signaling task executes is higher than that of the signaled task. In this case, a mechanism is needed to count each signaling occurrence. The counting semaphore provides just this facility. With a counting semaphore, the signaling task can continue to execute and increment a count at its own pace, while the wait task, when unblocked, executes at its own pace, as shown in Figure 6.7.

Figure 6.7: Credit-tracking synchronization between two tasks.

Again, the counting semaphore's count is initially 0, making it unavailable. The lower priority tWaitTask tries to acquire this semaphore but blocks until tSignalTask makes the semaphore available by performing a release on it. Even then, tWaitTask will waits in the ready state until the higher priority tSignalTask eventually relinquishes the CPU by making a blocking call or delaying itself, as shown in Listing 6.3.

Listing 6.3: Pseudo code for credit-tracking synchronization.

tWaitTask () {

:

Acquire counting semaphore token

:

}

tSignalTask () {

:

Release counting semaphore token

:

}

Because tSignalTask is set to a higher priority and executes at its own rate, it might increment the counting semaphore multiple times before tWaitTask starts processing the first request. Hence, the counting semaphore allows a credit buildup of the number of times that the tWaitTask can execute before the semaphore becomes unavailable.

Eventually, when tSignalTask's rate of releasing the semaphore tokens slows, tWaitTask can catch up and eventually deplete the count until the counting semaphore is empty. At this point, tWaitTask blocks again at the counting semaphore, waiting for tSignalTask to release the semaphore again.

Note that this credit-tracking mechanism is useful if tSignalTask releases semaphores in bursts, giving tWaitTask the chance to catch up every once in a while.

Using this mechanism with an ISR that acts in a similar way to the signaling task can be quite useful. Interrupts have higher priorities than tasks. Hence, an interrupt's associated higher priority ISR executes when the hardware interrupt is triggered and typically offloads some work to a lower priority task waiting on a semaphore.

- 6.4.1 Wait-and-Signal Synchronization

- Complex protocols and connection tracking

- 15.4 Resource Synchronization Methods

- 15.6.1 Synchronous Activity Synchronization

- 10.4 Synchronization and Messaging Tools

- 3.1. CLOCK SYNCHRONIZATION

- 3.1.3. Clock Synchronization Algorithms

- 6.4.8. Synchronization

- 10.2.3. Synchronization

- Chapter 15: Synchronization And Communication

- 5.6 Synchronization, Communication, and Concurrency

- 6.4.2 Multiple-Task Wait-and-Signal Synchronization