Книга: Real-Time Concepts for Embedded Systems

10.4.3 General Exception Priorities

10.4.3 General Exception Priorities

All processors handle exceptions in a defined order. Although not every silicon vendor uses the exact same order of exception processing, generally exceptions are handled according to these priorities, as shown in Table 10.2.

Table 10.2: Exception priorities.

| Highest | Asynchronous | Non-maskable |

| ? | Synchronous | Precise |

| Synchronous | Imprecise | |

| Lowest | Asynchronous | Maskable |

The highest priority level of exceptions is usually reserved for system resets, other significant events, or errors that warrant the overall system to reset. In many cases, hardware implementations for this exception also cause much, if not all, of the surrounding hardware to reset to a known state and condition. For this reason, this exception is treated as the highest level.

The next two priority levels reflect a set of errors and special execution conditions internal to the processor. A synchronous exception is generated and acknowledged only at certain states of the internal processor cycle. The sources of these errors are rooted in either the instructions or data that is passed along to be processed.

Typically, the lowest priority is an asynchronous exception external to the core processor. External interrupts (except NMIs) are the only exceptions that can be disabled by software.

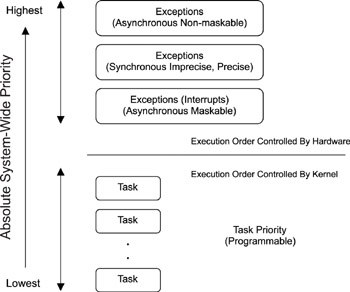

From an application point of view, all exceptions have processing priority over operating system objects, including tasks, queues, and semaphores. Figure 10.2 illustrates a general priority framework observed in most embedded computing architectures.

Figure 10.2: System-wide priority scheme.

- General

- 10.4 A Closer Look at Exceptions and Interrupts

- General concepts

- Выражения в EXCEPTION

- Appendix I. GNU General Public License

- 9.2.4. Traps, Exceptions, and Interrupts

- General Requirements

- General Security Considerations

- General Configuration Options Using the config File

- Using general-purpose commands

- Chapter 10: Exceptions and Interrupts

- 10.2 What are Exceptions and Interrupts?