Книга: Аппаратные интерфейсы ПК. Энциклопедия

7.1.1. Асинхронная память — FPM, EDO и BEDO DRAM

7.1.1. Асинхронная память — FPM, EDO и BEDO DRAM

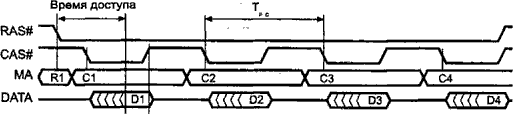

Временная диаграмма, приведенная на рис. 7.1, может быть модифицирована для случая последовательного обращения к ячейкам, принадлежащим к одной строке матрицы. В этом случае адрес строки выставляется на шине только один раз и сигнал RAS# удерживается на низком уровне на время всех последующих циклов обращений, которые могут быть как циклами записи, так и чтения. Такой режим обращения называется режимом быстрого страничного обмена FPM (Fast Page Mode), или просто режимом страничного обмена (Page Mode), его временная диаграмма приведена на рис. 7.2. Понятие «страница» на самом деле относится к строке (row), а состояние с низким уровнем сигнала RAS# называется «открытой страницей». Преимущество данного режима заключается в экономии времени за счет исключения фазы выдачи адреса строки из циклов, следующих за первым, что позволяет повысить производительность памяти. Режим FPM поддерживает и самая обычная асинхронная память, называемая стандартной (Std).

Рис. 7.2. Страничный режим считывания стандартной памяти DRAM (FPM

Память EDO DRAM (Extended или Enhanced Data Out) содержит регистр-защелку (data latch) выходных данных, что обеспечивает некоторую конвейеризацию работы для повышения производительности при чтении. Регистр «прозрачен» при низком уровне сигнала CAS#, а по его подъему фиксирует текущее значение выходных данных до следующего его спада. Перевести выходные буферы в высокоимпедансное состояние можно либо подъемом сигнала ОЕ# (Output Enable), либо одновременным подъемом сигналов CAS# и RAS#, либо импульсом WE#, который при высоком уровне CAS# не вызывает записи (в PC управление по входу ОЕ# практически не используют).

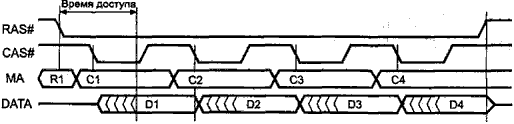

Временная диаграмма работы с EDO-памятью в режиме страничного обмена приведена на рис. 7.3; этот режим иногда называют гиперстраничным режимом обмена НРМ (Hyper Page mode). Его отличие от стандартного заключается в подъеме импульса CAS# до появления действительных данных на выходе микросхемы. Считывание выходных данных может производиться внешними схемами вплоть до спада следующего импульса CAS#, что позволяет экономить время за счет сокращения длительности импульса CAS#. Время цикла внутри страницы уменьшается, повышая производительность в страничном режиме на 40 %.

Рис. 7.3. Страничный режим считывания EDO DRAM (HPM)

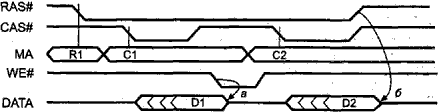

Установка EDO DRAM вместо стандартной памяти в неприспособленные для этого системы может вызвать конфликты выходных буферов устройств, разделяющих с памятью общую шину данных. Скорее всего, этот конфликт возникнет с соседним банком памяти при чередовании банков. Для отключения выходных буферов EDO-памяти внутри страничного цикла обычно используют сигнал WE#, не вызывающий записи во время неактивной фазы CAS# (рис. 7.4, кривая а). По окончании цикла буферы отключаются лишь по снятию сигнала RAS# (рис. 7.4, кривая б).

Рис. 7.4. Управление выходным буфером EDO DRAM

Из принципиального различия в работе выходных буферов следует, что в одном банке не стоит смешивать EDO и стандартные модули. EDO-модули поддерживаются не всеми чипсетами и системными платами (в большей мере это относится к системным платам для процессоров 486).

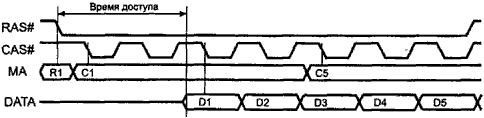

В памяти BEDO DRAM (Burst EDO) кроме регистра-защелки выходных данных, стробируемого теперь по фронту импульса CAS#, содержится еще и внутренний счетчик адреса колонок для пакетного цикла. Это позволяет выставлять адрес колонки только в начале пакетного цикла (рис. 7.5), а во 2-й, 3-й и 4-й передачах импульсы CAS# только запрашивают очередные данные. В результате удлинения конвейера выходные данные как бы отстают на один такт сигнала CAS#, зато следующие данные появляются без тактов ожидания процессора, чем обеспечивается лучший цикл чтения. Задержка появления первых данных пакетного цикла окупается повышенной частотой приема последующих. BEDO-память применяется в модулях SIMM-72 и DIMM, но поддерживается далеко не всеми чипсетами.

Рис. 7.5. Страничный режим считывания BEDO DRAM

Вышеперечисленные типы памяти являются асинхронными по отношению к тактированию системной шины компьютера. Это означает, что все процессы инициируются только импульсами RAS# и CAS#, а завершаются через какой-то определенный (для данных микросхем) интервал. На время этих процессоров шина памяти оказывается занятой, причем в основном ожиданием данных.

- Видеопамять

- 7.3.2. EEPROM и флэш-память

- Что хранит в себе оперативная память

- ЧАСТЬ 4 РАЗДЕЛЯЕМАЯ ПАМЯТЬ

- Глава 8 Оперативная память

- Кэш-память ЦП

- При запуске программы появляется сообщение Инструкция по адресу 0х77ddb1d1 обратилась к памяти по адресу 0x0080002c. Пам...

- 12.6. Обращение к объектам, отображенным в память

- 1.6.1. Как устроена оперативная память ПК?

- Как у вас с памятью?

- PART VI Fedora Housekeeping

- CHAPTER 1 Installing Fedora