Книга: Аппаратные интерфейсы ПК. Энциклопедия

1.3.3. Режим EPP

1.3.3. Режим EPP

Протокол EPP (Enhanced Parallel Port — улучшенный параллельный порт) был разработан компаниями Intel, Xircom и Zenith Data Systems задолго до принятия стандарта IEEE 1284. Этот протокол предназначен для повышения производительности обмена по параллельному порту, впервые был реализован в чипсете Intel 386SL (микросхема 82360) и впоследствии принят множеством компаний как дополнительный протокол параллельного порта. Версии протокола, реализованные до принятия IEEE 1284, отличаются от нынешнего стандарта (см. ниже).

Протокол EPP обеспечивает четыре типа циклов обмена:

? запись данных;

? чтение данных;

? запись адреса;

? чтение адреса.

Назначение циклов записи и чтения данных очевидно. Адресные циклы используются для передачи адресной, канальной и управляющей информации. Циклы обмена данными отличаются от адресных циклов применяемыми стробирующими сигналами. Назначение сигналов порта EPP и их связь с сигналами SPP объясняются в табл. 1.4.

Таблица 1.4. Сигналы LPT-порта в режиме ввода-вывода EPP

| Контакт | Сигнал SPP | Имя в EPP | I/O | Описание |

|---|---|---|---|---|

| 1 | Strobe# | Write# | O | Низкий уровень — цикл записи, высокий — цикл чтения |

| 14 | AutoLF# | DataStb# | O | Строб данных. Низкий уровень устанавливается в циклах передачи данных |

| 17 | SelectIn# | AddrStb# | O | Строб адреса. Низкий уровень устанавливается в адресных циклах |

| 16 | Init# | Reset# | O | Сброс ПУ (низким уровнем) |

| 10 | Ack# | INTR# | I | Прерывание от ПУ |

| 11 | Busy | Wait# | I | Сигнал квитирования. Низкий уровень разрешает начало цикла (установку строба в низкий уровень), переход в высокий — разрешает завершение цикла (снятие строба) |

| 2-9 | Data[0:7] | AD[0:7] | I/O | Двунаправленная шина адреса/данных |

| 12 | PaperEnd | AckDataReq? | I | Используется по усмотрению разработчика периферии |

| 13 | Select | Xflag? | I | Используется по усмотрению разработчика периферии |

| 15 | Error# | DataAvail#? | I | Используется по усмотрению разработчика периферии |

? Сигналы действуют в последовательности согласования (см. ниже).

EPP-порт имеет расширенный набор регистров (табл. 1.5), который занимает в пространстве ввода-вывода 5–8 смежных байт.

Таблица 1.5. Регистры EPP-порта

| Имя регистра | Смещение | Режим | R/W | Описание |

|---|---|---|---|---|

| SPP Data Port | +0 | SPP/EPP | W | Регистр данных SPP |

| SPP Status Port | +1 | SPP/EPP | R | Регистр состояния SPP |

| SPP Control Port | +2 | SPP/EPP | W | Регистр управления SPP |

| EPP Address Port | +3 | EPP | R/W | Регистр адреса EPP. Чтение или запись в него генерирует связанный цикл чтения или записи адреса EPP |

| EPP Data Port | +4 | EPP | R/W | Регистр данных EPP. Чтение (запись) генерирует связанный цикл чтения (записи) данных EPP |

| Not Defined | +5…+7 | EPP | N/A | В некоторых контроллерах могут использоваться для 16-32-битных операций ввода-вывода |

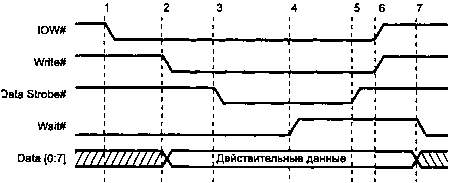

В отличие от программно-управляемых режимов, описанных выше, внешние сигналы EPP-порта для каждого цикла обмена формируются аппаратно по одной операции записи или чтения в регистр порта. На рис. 1.3 приведена диаграмма цикла записи данных, иллюстрирующая внешний цикл обмена, вложенный в цикл записи системной шины процессора (иногда эти циклы называют связанными). Адресный цикл записи отличается от цикла данных только стробом внешнего интерфейса.

Рис. 1.3. Цикл записи данных EPP

Цикл записи данных состоит из следующих фаз.

1. Программа выполняет цикл вывода (IOWR#) в порт 4 (EPP Data Port).

2. Адаптер устанавливает сигнал Write# (низкий уровень), и данные помещаются на выходную шину LPT-порта.

3. При низком уровне Wait# устанавливается строб данных.

4. Порт ждет подтверждения от ПУ (перевода Wait# в высокий уровень).

5. Снимается строб данных — внешний EPP-цикл завершается.

6. Завершается процессорный цикл вывода.

7. ПУ устанавливает низкий уровень Wait#, указывая на возможность начала следующего цикла.

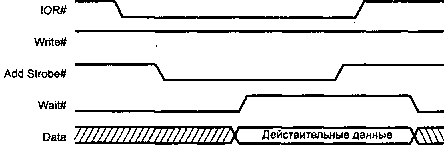

Пример адресного цикла чтения приведен на рис. 1.4. Цикл чтения данных отличается только применением другого стробирующего сигнала.

Рис. 1.4. Адресный цикл чтения EPP

Главной отличительной чертой EPP является выполнение внешней передачи во время одного процессорного цикла ввода-вывода. Это позволяет достигать высоких скоростей обмена (0,5–2 Мбайт/с). ПУ, подключенное к параллельному порту EPP, может работать со скоростью устройства, подключаемого через слот ISA.

Протокол блокированного квитирования (interlocked handshakes) позволяет автоматически настраиваться на скорость обмена, доступную и хосту, и ПУ. ПУ может регулировать длительность всех фаз обмена с помощью всего лишь одного сигнала Wait#. Протокол автоматически подстраивается под длину кабеля — вносимые задержки приведут только к удлинению цикла. Поскольку кабели, соответствующие стандарту IEEE 1284 (см. выше), имеют одинаковые волновые свойства для разных линий, нарушения передачи, связанного с «состязаниями» сигналов, происходить не должно. При подключении сетевых адаптеров или внешних дисков к EPP-порту можно наблюдать непривычное явление: снижение производительности по мере удлинения интерфейсного кабеля.

Естественно, ПУ не должно «подвешивать» процессор на шинном цикле обмена. Это гарантирует механизм тайм-аутов PC, который принудительно завершает любой цикл обмена, длящийся более 15 мкс. В ряде реализаций EPP за тайм-аутом интерфейса следит сам адаптер — если ПУ не отвечает в течение определенного времени (5 мкс), цикл прекращается и в дополнительном (нестандартизованном) регистре состояния адаптера фиксируется ошибка.

Устройства с интерфейсом EPP, разработанные до принятия IEEE 1284, отличаются началом цикла: строб DataStb# или AddrStb# устанавливается независимо от состояния WAIT#. Это означает, что ПУ не может задержать начало следующего цикла (хотя может растянуть его на требуемое время). Такая спецификация называется EPP 1.7 (предложена Xircom). Именно она применялась в контроллере 82360. Периферия, совместимая с IEEE 1284 EPP, будет нормально работать с контроллером EPP 1.7, но ПУ в стандарте EPP 1.7 может отказаться работать с контроллером EPP 1284.

С программной точки зрения контроллер EPP-порта выглядит просто (см. табл. 1.5). К трем регистрам стандартного порта, имеющим смещение 0, 1 и 2 относительно базового адреса порта, добавлены два регистра (EPP Address Port и EPP Data Port), чтение и запись в которые вызывает генерацию связанных внешних циклов.

Назначение регистров стандартного порта сохранено для совместимости EPP-порта с ПУ и ПО, рассчитанными на применение программно-управляемого обмена. Поскольку сигналы квитирования адаптером вырабатываются аппаратно, при записи в регистр управления CR биты 0, 1 и 3, соответствующие сигналам Strobe#, AutoFeed# и SelectIn# должны иметь нулевые значения. Программное вмешательство могло бы нарушить последовательность квитирования. Некоторые адаптеры имеют специальные средства защиты (EPP Protect), при включении которых программная модификация этих бит блокируется.

Использование регистра данных EPP позволяет осуществлять передачу блока данных с помощью одной инструкции REP INSB или REP OUTSB. Некоторые адаптеры допускают 16/32-битное обращение к регистру данных EPP. При этом адаптер просто дешифрует адрес со смещением в диапазоне 4–7 как адрес регистра данных EPP, но процессору сообщает о разрядности 8 бит. Тогда 16- или 32-битное обращение по адресу регистра данных EPP приведет к автоматической генерации двух или четырех шинных циклов по нарастающим адресам, начиная со смещения 4. Эти циклы будут выполняться быстрее, чем то же количество одиночных циклов. Более «продвинутые» адаптеры для адреса регистра данных EPP сообщают разрядность 32 бит и для них до 4 байт может быть передано за один цикл обращения процессора. Таким образом обеспечивается производительность до 2 Мбайт/с, достаточная для адаптеров локальных сетей, внешних дисков, стриммеров и CD-ROM. Адресные циклы EPP всегда выполняются только в однобайтном режиме.

Важной чертой EPP является то, что обращение процессора к ПУ осуществляется в реальном времени — нет буферизации. Драйвер способен отслеживать состояние и подавать команды в точно известные моменты времени. Циклы чтения и записи могут чередоваться в произвольном порядке или идти блоками. Такой тип обмена удобен для регистро-ориентированных ПУ или ПУ, работающих в реальном времени, например устройств сбора информации и управления. Этот режим пригоден и для устройств хранения данных, сетевых адаптеров, принтеров, сканеров и т.п.

К сожалению, режим EPP поддерживается не всеми портами — он отсутствует, к примеру, в ряде блокнотных ПК. Так что при разработке собственных устройств ради большей совместимости с компьютерами приходится ориентироваться на режим ECP.

- Резервное копирование при работе InterBase в режиме 24x7

- 8.5.3. Режимы энергосбережения

- Режим обратной совместимости

- 2.6. Термостабилизация режима каскада на биполярном транзисторе

- 33.1. Интерактивный и неинтерактивный режим работы

- 4. Режимы работы экспертных систем

- 1.1 Режимы ядра и пользователя Windows

- Работа с документами в режиме оффлайн

- Чем отличается спящий режим от ждущего?

- Можно ли при помощи горячих клавиш переводить компьютер в спящий режим?

- Рис. 94. Разрешить использование спящего режима.

- 3.4.1. Смена режима