Книга: Аппаратные интерфейсы ПК. Энциклопедия

12.3. Аппаратные прерывания

Аппаратные прерывания обеспечивают реакцию процессора на события, происходящие асинхронно по отношению к исполняемому программному коду. Прерывания в процессорах х86 подробно рассмотрены в литературе [6, 7]. Здесь напомним, что аппаратные прерывания делятся на маскируемые и немаскируемые.

На немаскируемое прерывание (NMI) процессор реагирует всегда (если обслуживание предыдущего NMI завершено); этому прерыванию соответствует фиксированный вектор 2. Немаскируемые прерывания в PC используются для сигнализации о фатальных аппаратных ошибках. Сигнал на линию NMI приходит от схем контроля паритета памяти, от линий контроля шины ISA (IOCHK) или шины PCI (SERR#). Сигнал NMI блокируется до входа процессора установкой в 1 бита 7 порта 070h, отдельные источники разрешаются и идентифицируются битами порта 061h:

? бит 2 R/W — ERP — разрешение контроля ОЗУ и сигнала SERR# шины PCI;

? бит 3 R/W — EIC — разрешение контроля шины ISA;

? бит 6 R — IOCHK — ошибка контроля на шине ISA (сигнал IOCHK#);

? бит 7 R — PCK — ошибка четности ОЗУ или сигнал SERR# на шине PCI.

Реакция процессора на маскируемые прерывания может быть задержана сбросом его внутреннего флага IF (инструкции СLI — запретить прерывания, STI — разрешить). По возникновении события, требующего реакции, адаптер (контроллер) устройства формирует запрос прерывания, который поступает на вход контроллера прерываний. Контроллер прерываний формирует общий запрос маскируемого прерывания для процессора, а когда процессор подтверждает этот запрос, контроллер сообщает процессору вектор прерывания, по которому выбирается программная процедура обработки прерываний. Процедура должна выполнить действия по обслуживанию данного устройства, включая сброс его запроса для обеспечения возможности реакции на следующие события и посылку команды завершения в контроллер прерываний. Вызывая процедуру обработки, процессор автоматически сохраняет в стеке значение всех флагов и сбрасывает флаг IF, что запрещает маскируемые прерывания. При возврате из процедуры (по инструкции IRET) процессор восстанавливает сохраненные флаги, в том числе и установленный IF, что снова разрешает прерывания. Если во время работы обработчика прерываний требуется реакция на иные прерывания (более приоритетные), то в обработчике должна присутствовать инструкция STI. Особенно это касается длинных обработчиков; здесь инструкция STI должна вводиться как можно раньше, сразу после критической (не допускающей прерываний) секции. Следующие прерывания того же или более низкого уровня приоритета контроллер прерываний будет обслуживать только после получения команды завершения прерывания EOI (End Of Interrupt).

Маскируемые прерывания используются для сигнализации о событиях в устройствах. Обработка сигналов запросов прерывания выполняется контроллером прерываний, программно совместимым с 8259A. Контроллер прерываний позволяет маскировать отдельные входы запросов и организовывать систему приоритетов запросов от различных входов. В машинах класса AT применяется каскадное соединение двух контроллеров. Ведущий контроллер 8259А#1 обслуживает запросы 0, 1, 3–7; его выход подключается к входу запроса прерываний процессора. К его входу 2 подключен ведомый контроллер 8259А#2, который обслуживает запросы 8-15. При этом поддерживается вложенность приоритетов — запросы 8-15 со своим рядом убывающих приоритетов вклиниваются между запросами 1 и 3 ведущего контроллера, приоритеты запросов которого также убывают с ростом номера. В XT каскадирование не применялось, и один контроллер 8259А обслуживал все 8 линий запросов.

Контроллер прерываний i8259A подробно описан в литературе [1, 7]; здесь приведем лишь необходимые сведения, в большинстве случаев достаточные для работы. Контроллеры расположены по адресам 20-21h (8259A#1) и A0-A1h (8259A#2), обращаться к ним следует как к однобайтным портам ввода-вывода. После инициализации (процедурой POST и при загрузке ОС) все неиспользуемые входы контроллеров замаскированы (на запросы прерываний реагировать не будут), а их векторы прерываний указывают на «заглушку» — процедуру с единственной инструкцией IRET. Первым делом программа должна загрузить в память свой обработчик и подставить указатель на его начало в соответствующее место таблицы прерываний. Далее следует размаскировать вход, для чего выполняется чтение регистра маски (адрес 21h для 8259А#1, A1h для 8259А#2), обнуление соответствующего бита (см. табл. 12.2) и запись в регистр нового значения маски. При работе с контроллером прерываний от программы требуется лишь управление маской своего запроса (при инициализации программы нужно обнулить маску требуемого запроса) и корректное завершение обработки прерываний. Каждая процедура обработки аппаратного прерывания должна завершаться командой EOI (End Of Interruption), посылаемой контроллеру:

? для 1-го контроллера — посылка байта 20h по адресу 20h;

? для 2-го контроллера — посылка байта 20h по адресу A0h (EOI для ведомого контроллера), затем посылка байта 20h по адресу 20h (EOI для ведущего контроллера).

Таблица 12.2. Аппаратные прерывания (в порядке убывания приоритета)

| Имя (номер?) | Вектор | Контроллер/маска | Описание |

|---|---|---|---|

| NMI | 02h | Контроль канала, паритет (в XT — сопроцессор) | |

| IRQ0 | 08h | #1/1h | Таймер (канал 0 8253/8254) |

| IRQ1 | 09h | #1/2h | Клавиатура |

| IRQ2 | 0Ah | #1/4h | XT — резерв, AT — недоступно (подключается каскад IRQ8-IRQ15) |

| IRQ8 | 70h | #2/1h | CMOS RTC — часы реального времени |

| IRQ9 | 71h | #2/2h | Резерв |

| IRQ10 | 72h | #2/4h | Резерв |

| IRQ11 | 73h | #2/8h | Резерв |

| IRQ12 | 74h | #2/10h | PS/2-Mouse (резерв) |

| IRQ 13 | 75h | #2/20h | Математический сопроцессор |

| IRQ14 | 76h | #2/40h | HDC — контроллер НЖМД |

| IRQ15 | 77h | #2/80h | Резерв |

| IRQ3 | 0Bh | #1/4h | COM2, COM4 |

| IRQ4 | 0Ch | #1/10h | COM1, COM3 |

| IRQ5 | 0Dh | #1/20h | XT — HDC, AT — LPT2, Sound (резерв) |

| IRQ6 | 0Eh | #1/40h | FDC — контроллер НГМД |

| IRQ7 | 0Fh | #1/80h | LPT1 — принтер |

? Запросы прерываний 0, 1, 8 и 13 на шины расширения не выводятся.

Некорректно завершенная процедура не позволит повторно использовать данный или другие запросы прерываний. Если обработчик прерывания удаляется из памяти, предварительно должен быть замаскирован соответствующий ему вход контроллера. Все изменения в таблице прерываний должны выполняться при замаскированных прерываниях, чтобы избежать попытки использования вектора в процессе его модификации (это приведет к «вылету» программы).

На входы контроллеров прерываний поступают запросы от системных устройств (клавиатура, системный таймер, CMOS-таймер, сопроцессор), периферийных контроллеров системной платы и от карт расширения. Традиционно все линии запросов, не занятые перечисленными устройствами, присутствуют на всех слотах шины ISA/EISA. Эти линии обозначаются как IRQx и имеют общепринятое назначение (табл. 12.2). Часть этих линий отдается в распоряжение шины PCI. В таблице отражены и приоритеты прерываний — запросы расположены в порядке их убывания. Номера векторов, соответствующих линиям запросов контроллеров, система приоритетов и некоторые другие параметры задаются программно при инициализации контроллеров. Эти основные настройки остаются традиционными для обеспечения совместимости с программным обеспечением.

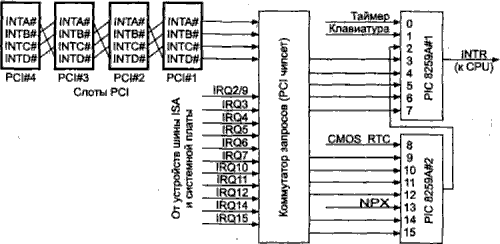

Для запросов прерывания с шины PCI используются 4 линии запросов прерывания, которые обозначают как INTR А, В, С, D. Эти линии работают по низкому уровню, что дает возможность их разделения (совместного использования). Линии циклически сдвигаются в слотах и независимо коммутируются на доступные линии IRQx с помощью конфигурационных регистров чипсета. Линии IRQx, используемые шиной PCI, становятся недоступными для шины ISA. «Дележку» линий между шинами, а также управление чувствительностью отдельных линий обеспечивают параметры CMOS Setup, а также система PnP. В параметрах ISA или Legacy подразумевают использование линий IRQx традиционными адаптерами шины ISA (статическое распределение), a PCI/PnP — использование адаптерами шины PCI или адаптерами PnP для шины ISA (динамическое распределение). Общая схема формирования запросов прерываний изображена на рис. 12.1.

Рис. 12.1. Коммутация запросов прерываний

Каждому устройству, для поддержки работы которого требуются прерывания, должен быть назначен свой номер прерывания. Назначения номеров прерываний выполняются с двух сторон: во-первых, адаптер, нуждающийся в прерываниях, должен быть сконфигурирован на использование конкретной линии шины (джамперами или программно). Во-вторых, программное обеспечение, поддерживающее данный адаптер, должно быть проинформировано о номере используемого вектора. В процессе назначения прерываний может участвовать система PnP для шин ISA и PCI, для распределения линий запросов между шинами служат специальные параметры CMOS Setup.

Контроллер прерываний позволяет программировать свои входы на чувствительность к уровню или перепаду сигнала.

? Чувствительность к уровню (level sensitive) означает, что контроллер прерываний вырабатывает запрос прерывания процессора по факту обнаружения определенного уровня (на ISA — высокого) на входе DRQx. Если к моменту завершения обработки этого запроса (после записи команды EOI в регистр контроллера прерываний) контроллер снова обнаруживает активный уровень на том же входе DRQx, то он снова сформирует запрос на прерывание процессора.

? Чувствительность к перепаду (edge sensitive) означает, что контроллер прерываний вырабатывает запрос прерывания процессора только по факту обнаружения перепада (на ISA — положительного) на входе DRQx. Повторно запрос по этому входу возможен только по следующему такому же перепаду, то есть сигнал предварительно должен вернуться в исходное состояние.

В любом случае сигнал запроса аппаратного прерывания IRQx должен удерживаться генерирующей его схемой, по крайней мере, до цикла подтверждения прерывания процессором. В противном случае источник прерывания корректно идентифицирован не будет, и контроллер сообщит ложный вектор прерывания (spurious interrupt), соответствующий его входу с максимальным номером (IRQ7 для первого контроллера и IRQ15 для второго). Обычно адаптеры строят так, что сигнал запроса сбрасывается при обращении программы обслуживания прерывания к соответствующим регистрам адаптера.

В шине ISA прерывание вырабатывается по положительному перепаду сигнала на линии запроса. Это плохо по двум причинам: такой способ подачи сигнала, во-первых, имеет меньшую помехозащищенность, чем срабатывание по отрицательному перепаду, во-вторых, отрезает путь к нормальному разделению линий запросов (см. ниже), для которого полностью пригоден способ подачи сигнала по низкому уровню. Поскольку традиционный контроллер позволяет задавать чувствительность — уровень (Level) или перепад (Edge) — только для всех входов одновременно, в общем случае разделяемые прерывания на шине ISA вместе с корректной работой системных устройств использоваться не могут.

На современных системных платах функции контроллеров прерываний возлагаются на чипсет, который может иметь и более гибкие возможности управления, чем пара контроллеров 8259A. В операционном режиме всегда сохраняется программная совместимость с 8259A. Процедура инициализации контроллеров может и отличаться от традиционной, но ею занимается тест POST, который «знает» особенности системной платы. В симметричных мультипроцессорных системах аппаратные прерывания работают сложнее, поскольку их могут обслуживать различные процессоры. Для реализаций системы прерываний процессоры Pentium и выше имеют встроенный контроллер прерываний APIC (Advanced Programmable Interruption Controller). Внутренние контроллеры процессоров связаны между собой по шине APIC, к которой подключена и «ответная часть» чипсета, преобразующая запросы аппаратных прерываний в сигналы протокола APIC. В операционном режиме такая связка также совместима с 8259A.

- 12.8. Сервисы и прерывания BIOS

- Прерывания

- 6.1.5. Прерывания

- Информатика: аппаратные средства персонального компьютера

- Часть I Аппаратные средства персональных компьютеров

- Подпрограмма обработки прерывания

- 5.2. Структура и аппаратные средства современного персонального компьютера

- 6 Раздражающие прерывания

- 10.6.6. Создание возможности для прерывания функций: siginterrupt()

- Подсистема прерывания контроллера msCAN12.

- Глава 6 Прерывания и обработка прерываний

- Регистрация обработчика прерывания