Книга: Аппаратные интерфейсы ПК. Энциклопедия

7.2. Статическая память

7.2. Статическая память

Статическая память — SRAM (Static Random Access Memory), как и следует из ее названия, способна хранить информацию в статическом режиме — то есть сколь угодно долго при отсутствии обращений (но при наличии питающего напряжения). Ячейки статической памяти реализуются на триггерах — элементах с двумя устойчивыми состояниями. По сравнению с динамической памятью эти ячейки более сложные и занимают больше места на кристалле, однако они проще в управлении и не требуют регенерации. Быстродействие и энергопотребление статической памяти определяется технологией изготовления и схемотехникой запоминающих ячеек.

Асинхронная статическая память (Asynchronous SRAM, Async SRAM), она же обычная, или стандартная, подразумевается под термином SRAM по умолчанию, когда тип памяти не указан.

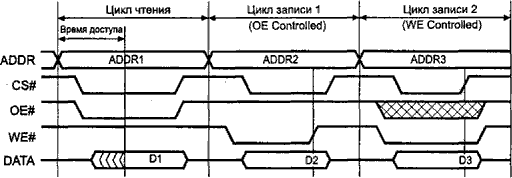

Микросхемы этого типа имеют простейший асинхронный интерфейс, включающий шину адреса, шину данных и сигналы управления CS#, ОЕ# и WE#. Микросхема выбирается низким уровнем сигнала CS# (Chip select), низкий уровень сигнала ОЕ# (Output Enable) открывает выходные буферы для считывания данных, WE# (Write Enable) низким уровнем разрешает запись. Временные диаграммы циклов обращения приведены на рис. 7.17. При операции записи управление выходными буферами может производиться как сигналом ОЕ# (цикл 1), так и сигналом WE# (цикл 2). Для удобства объединения микросхем внутренний сигнал CS# может собираться по схеме «И» из нескольких внешних, например CS0#, CS1# и CS2# — в таком случае микросхема будет выбрана при сочетании логических сигналов 0, 1, 0 на соответствующих входах.

Рис. 7.17. Временные диаграммы чтения и записи асинхронной статической памяти

Время доступа — задержка появления действительных данных на выходе относительно момента установления адреса — у стандартных микросхем SRAM составляет 12, 15 или 20 наносекунд, что позволяет процессору выполнять пакетный цикл чтения 2-1-1-1 (то есть без тактов ожидания) на частоте системной шины до 33 МГц. На более высоких частотах цикл будет не лучше 3-2-2-2.

Синхронная пакетная статическая память, Sync Burst SRAM, оптимизирована под выполнение пакетных (burst) операций обмена, свойственных кэш-памяти. В ее структуру введен внутренний двухбитный счетчик адреса (не позволяющий перейти границу четырехэлементного пакетного цикла). В дополнение к сигналам, характерным для асинхронной памяти (адрес, данные, CS#, OE# и WE#), синхронная память использует сигнал CLC (Clock) для синхронизации с системной шиной и сигналы управления пакетным циклом ADSP#, CADS# и ADV#. Сигналы CADS# (Cache ADdress Strobe) и ADSP# (ADdress Status of Processor), которыми процессор или кэш-контроллер отмечает фазу адреса очередного цикла, являются стробами записи начального адреса цикла во внутренний регистр адреса. Любой из этих сигналов инициирует цикл обращения, одиночный (single) или пакетный (burst), а сигнал ADV# (ADVance) используется для перехода к следующему адресу пакетного цикла. Все сигналы, кроме сигнала управления выходными буферами ОЕ#, синхронизируются по положительному перепаду сигнала CLK. Это означает, что значение входных сигналов должно установиться до перепада и удерживаться после него еще некоторое время. Выходные данные при считывании будут также действительны во время этого перепада. Микросхемы синхронной статической памяти, как и SDRAM, обычно имеют сигнал, выбирающий режим счета адреса: чередование (для процессоров Intel) или последовательный счет (для Power PC).

Конвейерно-пакетная статическая память, PB SRAM (Pipelined Burst SRAM), — усовершенствование синхронной памяти (слово «синхронная» из ее названия для краткости изъяли, но оно обязательно подразумевается). Конвейером является дополнительный внутренний регистр данных, который, требуя дополнительного такта в первой пересылке цикла, позволяет остальные данные получать без тактов ожидания даже на частотах выше 75 МГц. Задержка данных относительно синхронизирующего перепада у современных микросхем PB SRAM составляет 4,5–8 нс! Но, как и в случае Sync Burst SRAM, этот параметр не является временем доступа в чистом виде (не следует забывать о двух-трех тактах в первой передаче), а отражает появление действительных данных относительно очередного перепада сигнала синхронизации. Интерфейс PB SRAM аналогичен интерфейсу Sync Burst SRAM.

- Управление памятью (memory management) и сборка мусора (garbage collection)

- Статическая типизация (static typing)

- Видеопамять

- 7.3.2. EEPROM и флэш-память

- Что хранит в себе оперативная память

- ЧАСТЬ 4 РАЗДЕЛЯЕМАЯ ПАМЯТЬ

- Глава 8 Оперативная память

- Кэш-память ЦП

- При запуске программы появляется сообщение Инструкция по адресу 0х77ddb1d1 обратилась к памяти по адресу 0x0080002c. Пам...

- 12.6. Обращение к объектам, отображенным в память

- 1.6.1. Как устроена оперативная память ПК?

- Как у вас с памятью?