Книга: Аппаратные интерфейсы ПК. Энциклопедия

8.1.1. Интерфейс клавиатуры AT и PS/2

8.1.1. Интерфейс клавиатуры AT и PS/2

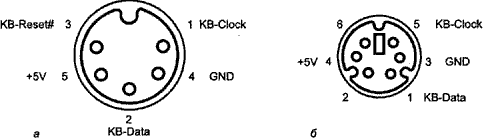

Для подключения клавиатуры предназначен последовательный синхронный двунаправленный интерфейс, состоящий из двух обязательных сигналов KB-Data и KB-Clock. Обе линии на системной плате подтягиваются резисторами к шине +5 В. На обеих сторонах интерфейса выходные сигналы низкого уровня формируются выходами элементов с открытым коллектором (стоком), а состояние линий может быть прочитано через входные линии контроллеров. Вид разъемов (со стороны задней панели) и назначение контактов приведены на рис. 8.1. Конструктивно возможны два варианта разъема — обычная 5-контактная розетка DIN (клавиатура AT) или малогабаритная розетка mini-DIN (PS/2). На этот же разъем через плавкий предохранитель поступает напряжение питания клавиатуры +5 В.

Рис. 8.1. Разъемы (вид со стороны контактов) подключения клавиатур: а — AT и б — PS/2

ВНИМАНИЕ

Питание от разъема клавиатуры часто используется такими устройствами, как внешние накопители или адаптеры локальных сетей, подключаемыми к параллельному порту. Плавкий предохранитель, установленный на системной плате, может не выдержать броска тока, потребляемого этими устройствами. При этом откажется работать и клавиатура — ее индикаторы даже и не мигнут при включении.

Процессор общается с клавиатурой через контроллер интерфейса клавиатуры — микроконтроллер 8042 или программно-совместимый с ним, установленный на системной плате. Для обмена информацией в основном используется порт 60h, из которого принимаются скан-коды. О необходимости чтения скан-кода контроллер сигнализирует процессору через аппаратное прерывание IRQ1, сигнал которого вырабатывается по каждому событию клавиатуры (нажатию и отпусканию клавиши). Задание параметров автоповтора, выбор таблиц скан-кодов, управление светодиодными индикаторами, а также управление режимом сканирования матрицы клавиш и запуск диагностического теста осуществляется командами, посылаемыми в этот же порт. Контроллер транслирует команды в посылки, направляемые к клавиатуре.

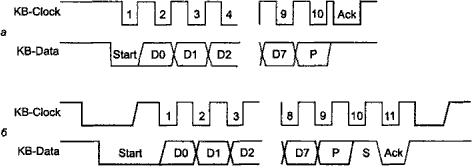

Работу двунаправленного интерфейса иллюстрирует рис. 8.2, а, где серым цветом помечены сигналы, формируемые контроллером, а черным — клавиатурой. В исходном состоянии обе линии «отпущены» выходными формирователями в состояние с высоким уровнем. Клавиатура может начать передачу данных в произвольный момент, когда интерфейс находится в покое. Клавиатура формирует стартовый бит (низкий уровень) на линии KB-Data и первый импульс KB-Clock, что является сигналом контроллеру о необходимости начала приема. После подъема KB-Clock она выводит 0-й бит данных на линию KB-Data, а затем и следующий импульс KB-Clock. Контроллер должен «защелкивать» принятый бит данных по спаду KB-Clock. Так передаются все 8 бит данных и бит паритета, дополняющий число единичных бит до нечетного. После синхроимпульса бита паритета контроллер клавиатуры должен сформировать импульс KB-Clock, подтверждающий прием байта (Ack). Если весь байт с битом паритета не будет получен контроллером за 2 мс, контроллер прекращает прием данного байта и фиксирует ошибку тайм-аута.

Рис. 8.2. Временные диаграммы интерфейса клавиатуры: а — прием посылки от клавиатуры, б — передача команды в клавиатуру

Обратная передача — вывод команды контроллера в клавиатуру — происходит несколько сложнее (рис. 8.2, б). Из состояния покоя контроллер устанавливает низкий уровень KB-Clock на 250 мкс и формирует старт-бит (низкий уровень) — это сигнал клавиатуре на прием команды. На него клавиатура должна ответить серией из 11 импульсов KB-Clock. По спаду очередного синхроимпульса контроллер выставляет очередной бит данных, а клавиатура его «защелкивает» по фронту формируемого ею же синхроимпульса. После бита паритета (9-й импульс) и единичного стоп-бита (10-й) на 11-м импульсе клавиатура формирует нулевой бит подтверждения (Ack). После этого контроллер формирует импульс KB-Clock (60 мкс), который является запросом на прием ответа клавиатуры. Контроллер ожидает окончания ответа на этот запрос не долее 20 мс и, если ответ не придет за это время, сформирует ошибку тайм-аута. Ошибка будет также в случае, если клавиатура не введет первый синхроимпульс за 15 мс от начала запроса или контроллер не примет данные, включая стоп-бит, за 2 мс с момента появления синхроимпульса бита 0.

На системной плате PC/XT контроллера 8042 не было, а интерфейс клавиатуры (однонаправленный) был реализован аппаратной логикой — регистром сдвига, параллельный выход которого подключается к входам порта А системного интерфейса 18255. По приему байта от клавиатуры вырабатывается аппаратное прерывание IRQ1, обработчик которого может прочитать принятый байт из порта 60h. С помощью бит 7 и 6 порта 61h возможны программная блокировка и сброс клавиатуры соответственно. Сброс клавиатуры XT осуществляется обнулением линии KB-Clock.

- Профилактика поломок клавиатуры

- Глава 8 Специализированные интерфейсы периферийных устройств

- 8.1. Интерфейс клавиатуры

- 8.1.1. Интерфейс клавиатуры AT и PS

- 8.1.2. Контроллер интерфейса клавиатуры и мыши 8042

- 8.1.3. Системная поддержка и программный интерфейс

- 8.2. Интерфейсы мыши

- 8.2.2. Мышь PS

- 12.8.1. Int 09h, Int 16h — поддержка клавиатуры

- 4.3.1. Производительность интерфейса для Хола

- 15.3. Слушание уведомлений, поступающих с клавиатуры, и реагирование на них

- 12. Лекция: Создание приложений с графическим интерфейсом пользователя.